请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TS3L301 主题中讨论的其他器件:TS5MP646

大家好、

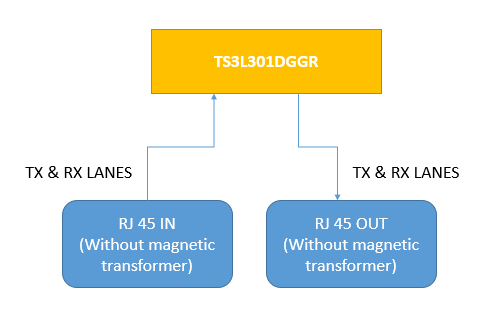

我们计划在 项目中将 TS3L301DGGR 器件用作模拟开关。 我们使用 TS3L301DGGR 打开和关闭 RJ 45 in 和 RJ 45 out 之间的 TX/RX 通道 、如下图所示。

您能否帮助我们、如果我们使用两层 PCB、而不在 RJ45的 TX 和 RX 通道的 PCB 中维持控制阻抗、会出现什么问题? 请告诉我、信号通道中是否会有数据丢失? 我们不在 RJ 45和模拟开关之间使用磁性变压器。

如果您还让我知道在没有磁性变压器的情况下、RJ45 (1000B-T)的每个通道中将有什么电流流动、那将非常有帮助。 我发现的导通状态开关电流为 TS3L301DGGR +/- 128mA。 是否建议使用 TS3L301DGGR IC?

此致、

Harshavardhan.K