我正在尝试找出电路板上 CC3220MODSF 首次启动问题的根本原因。

摘要:使用未编程的模块组装电路板。 在生产测试中、串行闪存(在模块中)是已编程的、而复位保持低电平有效、并且编程完成后、复位被置为无效。 延迟一段时间后、允许模块启动、会向 Wi-Fi 模块发送一些命令以检查其是否处于活动状态。 为了简化测试,我使用了两条命令,一条是读取 MAC 地址,另一条是在每个操作之间存在一定延迟的循环中完成的 Clock_getTicks()。 那么、Wi-Fi 模块不响应的可能性是有限的。 这意味着在电路板上运行相同的测试100次、测试的可变百分比将失败。

更多详细信息:

串行闪存通过 SPI 编程、如 swra568中的第4章所述。 编程通过测试针完成。 编程完成后、缓冲区将设置为 high-z

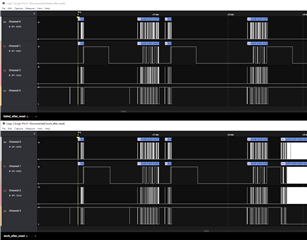

当模块复位无效时、我已经监控了 SPI 总线。 通道0为 FLASH_SPI_clk 、通道1复位。 这通常在模块没有响应时发生:

SPI 总线在2.5ms 内有效、这意味着永远不会读取串行闪存的内容。

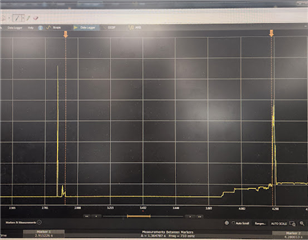

在这种情况下、我发现执行额外复位有助于:

SPI 总线上的前2.5ms 与第一幅图完全相同。 首次引导后看到的 SPI 总线脉冲是读取 MAC 地址时的脉冲。 "Clock_getTicks()"将每秒返回0x6。

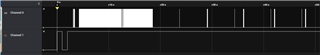

插入3. 复位:

每次调用该模块时,该模块都会返回预期的 Clock_getTicks()值,读取 MAC 地址时,该模块在 SPI 总线上没有通信。

有人能否解释为什么 Wi-Fi 模块在某些情况下需要额外的复位才能启动? 如果复位时间太短、也会失败。