Thread 中讨论的其他器件:WL1831

您好!

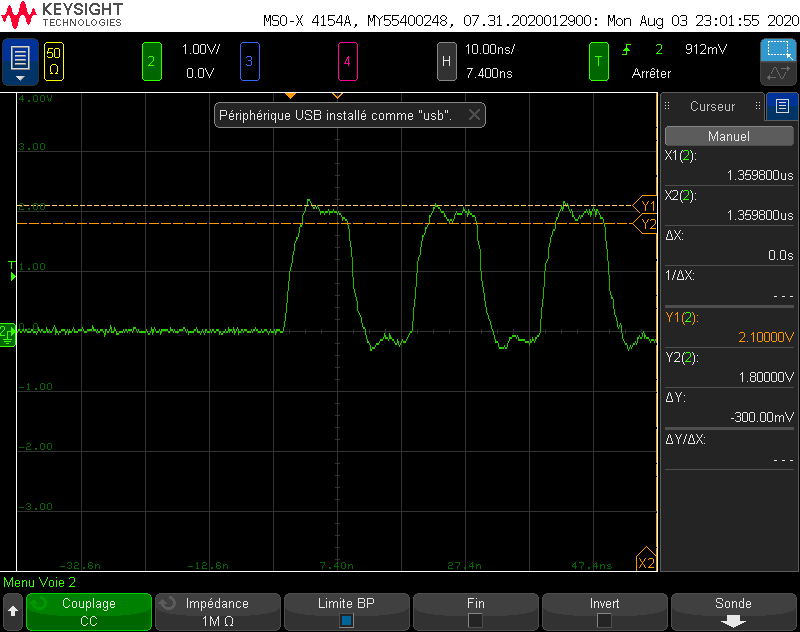

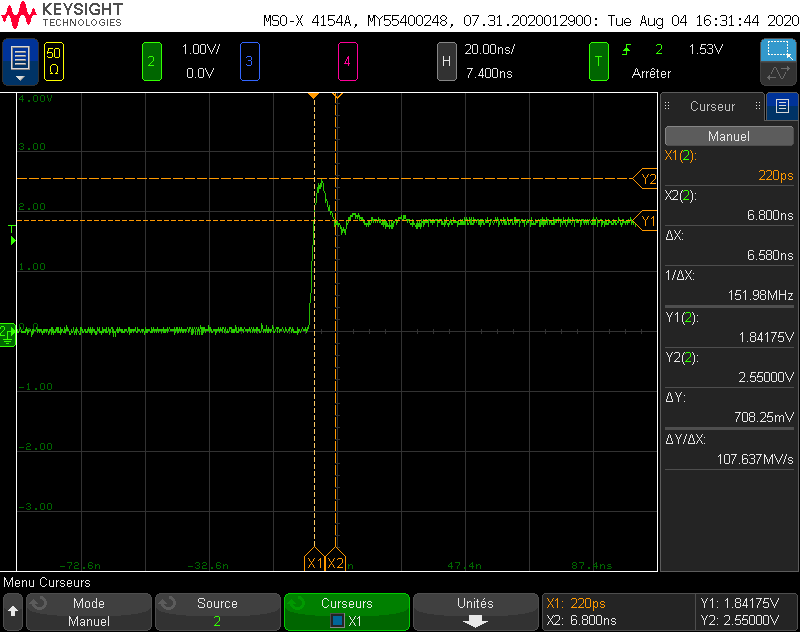

通过检查 WL1381MOD 的 SDIO (WiFi HCI)和 UART (BT HCI)输入上的信号完整性、我们发现在1.8V = Vio 的基础上、一些过冲/下冲为0.5~0.6V。 对于33R 系列分辨率、它们被限制在0.3V。

数据表相当严格:

-绝对最大 值:CLK_IN (SDIO 时钟)的 VDD_IO 和其他引脚的 VDD_IO+0.5V。

-建议 值: 最大 VIH = VDD_IO

如果我们进一步增大串联电阻、我们就害怕降低上升时间并获得不够陡的时钟或数据 上升...

问题: 考虑到该过冲/下冲只是瞬态违反规范,是否可以接受该0.3V 过冲/下冲? 这是否会真正影响 WL1831的长期可靠性?

非常感谢您的支持

Thomas