工具与软件:

Champs,

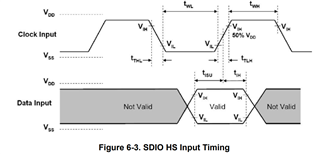

在设计验证过程中、客户会检查接口信号。 一个问题与 CLK 上升沿之前输入数据信号的设置时序有关。 下图显示了 WIFI (蓝色)上的 CLK (黄色)和 D3 Data 信号:

下表是与数据表中的预期测量值进行比较的其他数据信号:

|

参数 |

呈指数衰减 |

测量的 D0 |

测量 D1 |

测量的 D2 |

测量 D3 |

|

时钟频率、CLK |

< 52MHz |

48.04MHz |

48.01MHz |

47.96MHz |

47.93MHz |

|

高电平周期 |

>7ns. |

8.48ns |

8.56ns |

8.32ns |

8.56ns |

|

低电平周期 |

>7ns. |

8.32ns |

8.36ns |

8.48ns |

8.4ns |

|

上升时间、CLK |

<3ns |

2.16ns |

2.12ns |

2.12ns |

2.04ns |

|

下降时间、CLK |

<3ns |

1.96ns |

1.8ns |

1.76ns |

1.84ns |

|

建立时间、在 CLK↑前输入有效 |

>6ns |

3.2ns |

3.28ns |

3.72ns |

3.08ns |

|

保持时间、在 CLK↑后输入有效 |

>2ns. |

3.44ns |

3.48ns |

3.4ns |

3.48ns |

从捕获结果来看、似乎很难达到大于6ns 的设置时间规格、是否有任何屏幕捕获或测试数据可供客户参考?

数据信号也显示出一些不对称、这也是在预料之中吗? 如果您对此也有疑虑、我们希望您能就可能导致此问题的原因以及如何改进此问题发表意见

谢谢你

Michael