其中CLB以PWM1 TBCTR=Zero作为全局输入,通过修改Count0的match2修改占空比PWM2通过修改CMPA修改占空比。

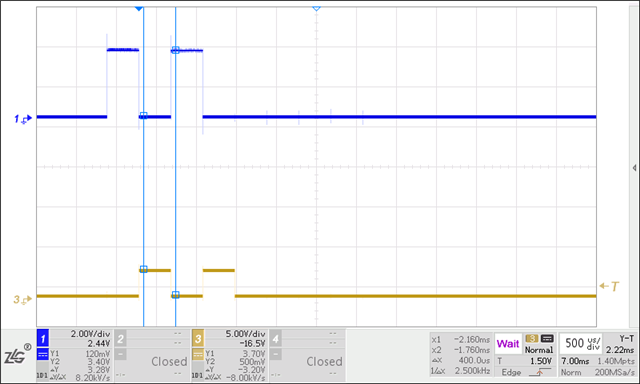

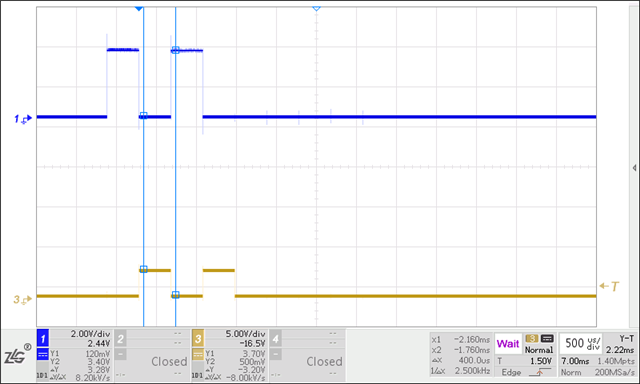

定时器每200us同时修改Count0的match2和CMPA,生成两次满占空比的脉冲,完成后输出低电平。如图所示:

CLB和PWM2同时修改计数值,应该同时发出两个脉冲,但是CLB比PWM2慢一周期这是为什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

其中CLB以PWM1 TBCTR=Zero作为全局输入,通过修改Count0的match2修改占空比PWM2通过修改CMPA修改占空比。

定时器每200us同时修改Count0的match2和CMPA,生成两次满占空比的脉冲,完成后输出低电平。如图所示:

CLB和PWM2同时修改计数值,应该同时发出两个脉冲,但是CLB比PWM2慢一周期这是为什么?

可以,这个是SYSCFG配置文件,麻烦看看。tupian.zip

您能描述一下FSM配置以及您希望它做什么吗?我假设这些用于将计数器事件转换为PWM边缘,但我很难理解状态方程。