Other Parts Discussed in Thread: TMDSCNCD28388D

首先device.h里面添加的符合10MHz晶振源的时钟链应该是没问题的,如下。

//

// 10MHz XTAL on eRob-Master. For use with SysCtl_getClock() and

// SysCtl_getAuxClock().

//

#define DEVICE_OSCSRC_FREQ 10000000U

//

// Define to pass to SysCtl_setClock(). Will configure the clock as follows:

// PLLSYSCLK = 10MHz (XTAL_OSC) * 80 (IMULT) / (2 (REFDIV) * 2 (ODIV) * 1(SYSDIV))

//

#define DEVICE_SETCLOCK_CFG (SYSCTL_OSCSRC_XTAL_SE | SYSCTL_IMULT(80) | \

SYSCTL_REFDIV(2) | SYSCTL_ODIV(2) | \

SYSCTL_SYSDIV(1) | SYSCTL_PLL_ENABLE | \

SYSCTL_DCC_BASE_1)

//

// 200MHz SYSCLK frequency based on the above DEVICE_SETCLOCK_CFG. Update the

// code below if a different clock configuration is used!

//

#define DEVICE_SYSCLK_FREQ ((DEVICE_OSCSRC_FREQ * 80) / (2 * 2 * 1))

//

// 50MHz LSPCLK frequency based on the above DEVICE_SYSCLK_FREQ and a default

// low speed peripheral clock divider of 4. Update the code below if a

// different LSPCLK divider is used!

//

#define DEVICE_LSPCLK_FREQ (DEVICE_SYSCLK_FREQ / 4)

//

// Define to pass to SysCtl_setAuxClock(). Will configure the clock as follows:

// AUXPLLCLK = 10MHz (XTAL_OSC) * 50 (IMULT) / (2 (REFDIV) * 2 (ODIV) * 1(AUXPLLDIV) )

//

#define DEVICE_AUXSETCLOCK_CFG (SYSCTL_AUXPLL_OSCSRC_XTAL | SYSCTL_AUXPLL_IMULT(50) | \

SYSCTL_REFDIV(2U) | SYSCTL_ODIV(2U) | \

SYSCTL_AUXPLL_DIV_1 | SYSCTL_AUXPLL_ENABLE | \

SYSCTL_DCC_BASE_0)

//

// 125MHz AUXCLK frequency based on the above DEVICE_AUXSETCLOCK_CFG. Update

// the code below if a different clock configuration is used!

//

#define DEVICE_AUXCLK_FREQ ((DEVICE_OSCSRC_FREQ * 50) / (2 * 2 * 1))

前面三项测试runParityTest、runCorrectableECCTest、runUncorrectableECCTest都正确通过,故障关键是runESCRAMParityTest测试项目里的ESCSS_initMemory(ESC_SS_BASE);

该步骤未能真实启动ESCSS。

直接用例程测试没通过,下面是我添加了测试标记的runESCRAMParityTest函数。

//

// runESCRAMParityTest - Runs a test of the parity logic in the ESC RAM.

//

uint32_t AUX_Clock_Freq;

uint16_t RegEscClk;

uint16_t runESCRAMParityTest(void)

{

uint16_t fail = 0U;

volatile uint32_t temp;

uint16_t timeout = ISR_LOOP_TIMEOUT;

//

// Initialize the EtherCAT clock and ESC RAM just enough to be able to test

// the parity logic. See the EtherCAT-specific examples for the full

// configuration (in libraries/communications/Ethercat).

//

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_ECAT);

SysCtl_setECatClk(SYSCTL_ECATCLKOUT_DIV_1, SYSCTL_SOURCE_AUXPLL, 1);

SysCtl_resetPeripheral(SYSCTL_PERIPH_RES_ECAT);

asm(" RPT #5 || NOP");

EALLOW;

AUX_Clock_Freq = SysCtl_getAuxClock(10000000);

RegEscClk = HWREGH(CLKCFG_BASE + SYSCTL_O_ETHERCATCLKCTL);

ESCSS_initMemory(ESC_SS_BASE);

EDIS;

ESTOP0;

if(ESCSS_getMemoryInitDoneStatusBlocking(ESC_SS_BASE, ETHERCAT_RAM_TIMEOUT) !=

ESCSS_API_SUCCESS)

{

fail++;

}

//

// Introduce a parity error.

//

EALLOW;

HWREG(MEMCFG_BASE + MEMCFG_O_PERI_MEM_TEST_CONTROL) =

MEMCFG_PERI_MEM_TEST_CONTROL_ETHERCAT_MEM_FORCE_ERROR;

EDIS;

//

// Clear error status variables.

//

nmiISRFlag = false;

nmiStatus = 0U;

errorAddr = 0U;

//

// Read a location in the ESC RAM to detect the error.

//

temp = HWREGH(ETHERCAT_RAM_ADDR);

EALLOW;

// Clear the parity error.

HWREG(MEMCFG_BASE + MEMCFG_O_PERI_MEM_TEST_CONTROL) = 0U;

// Reset memory, turn off ESC base.

HWREGH(ESC_SS_BASE + ESCSS_O_MEM_TEST) = 0U;

EDIS;

//

// Wait until the error interrupt is fired.

//

while((nmiISRFlag != true) && (timeout != 0U))

{

timeout--;

}

//

// Check if interrupt occurred as expected or if the loop timed out.

//

if(timeout == 0U)

{

fail++;

}

//

// Check if the NMI triggered was due to an uncorrectable RAM error.

//

if((nmiStatus & SYSCTL_NMI_RAMUNCERR) != SYSCTL_NMI_RAMUNCERR)

{

fail++;

}

return(fail);

}

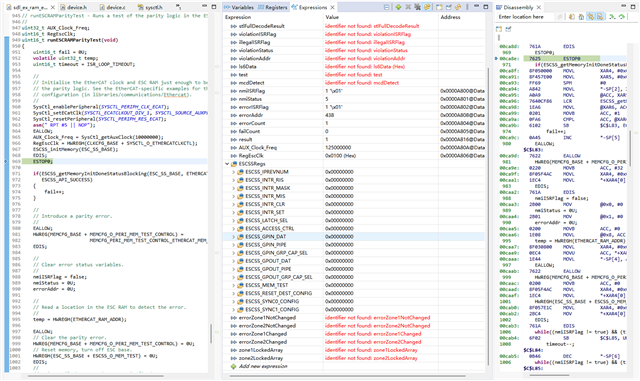

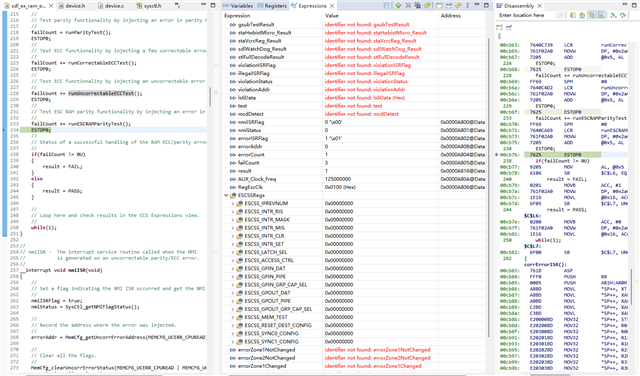

调试表现如下图。左边为刚执行完ESCSS_initMemory的样子,右边为跑完runESCRAMParityTest的样子。

你觉得是什么原因造成了ESCSS启动失败,有没有可能ESC_SS_BASE的值有问题?