Part Number: TMS320F280034

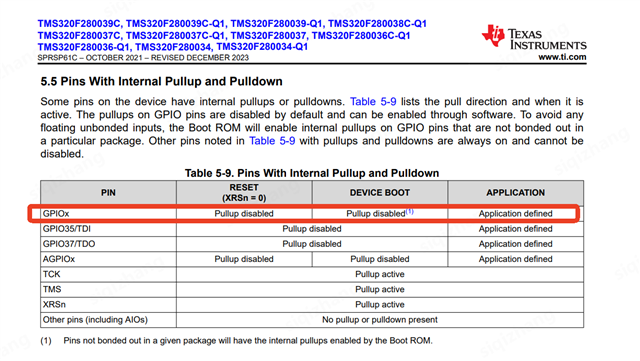

在数据手册(图 1:5.5 带有内部上拉和下拉的引脚 )中说明,复位后,GPIO 引脚上的上拉默认是禁用的。

我烧录程序时,发现某个GPIO会有拉高现象,如波形所示,与外部电路完全断开后测得实际引脚输出的是3.3V。该引脚一直拉高,直到程序运行到main函数中gpio初始化的部分。

此后我进行了在线仿真,程序烧录时仍然有此现象,在程序运行前如下图,GPBPUD寄存器并非全为 1 ,使几个 IO 口输出高电平。单步运行到初始化的代码时,GPBPUD 寄存器才会变为上拉禁用的状态。

为什么这个现象与手册中的描述不符合?在芯片复位到程序运行这段不受控的时间内,如何确保我的GPIO输出为低?目前策略是将该引脚换用至初始化后显示禁用的引脚上,但不确定是否可靠?

请帮助我,谢谢。