Part Number: TMS320F28377D

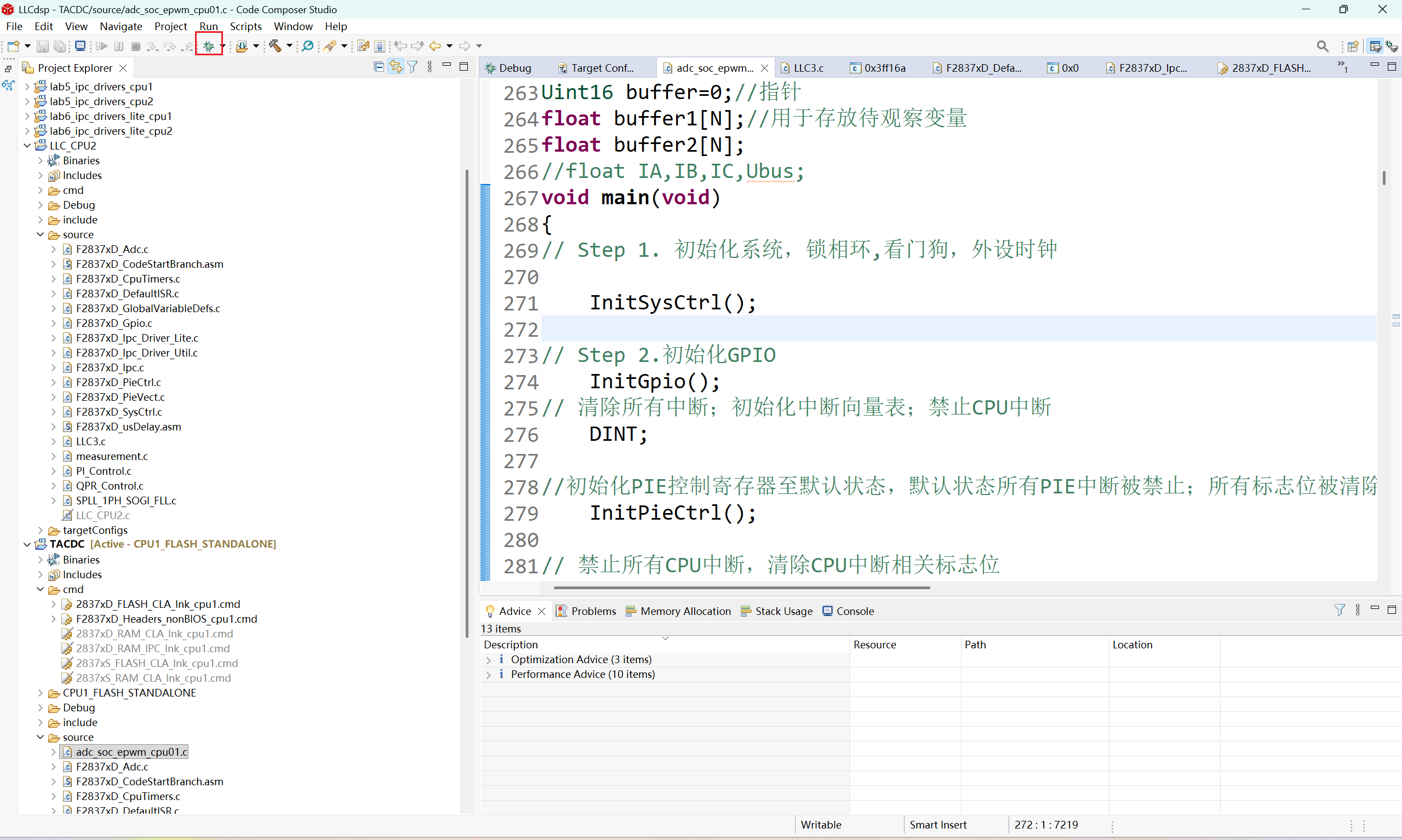

这是我现在cpu1用的cmd文件代码,现在出现的问题是但我直接点击debug时,能够正常进入cla中断中如图 。

。

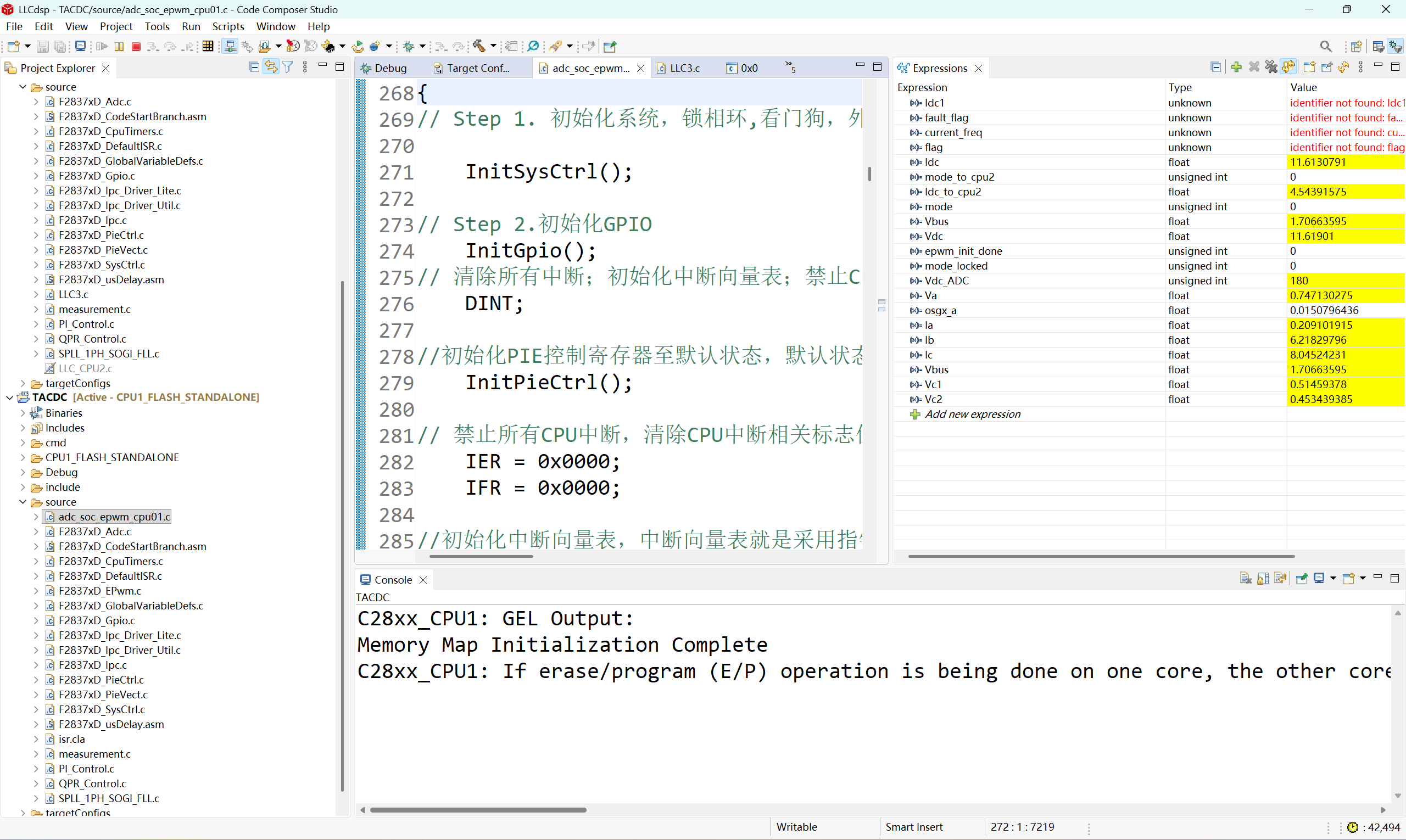

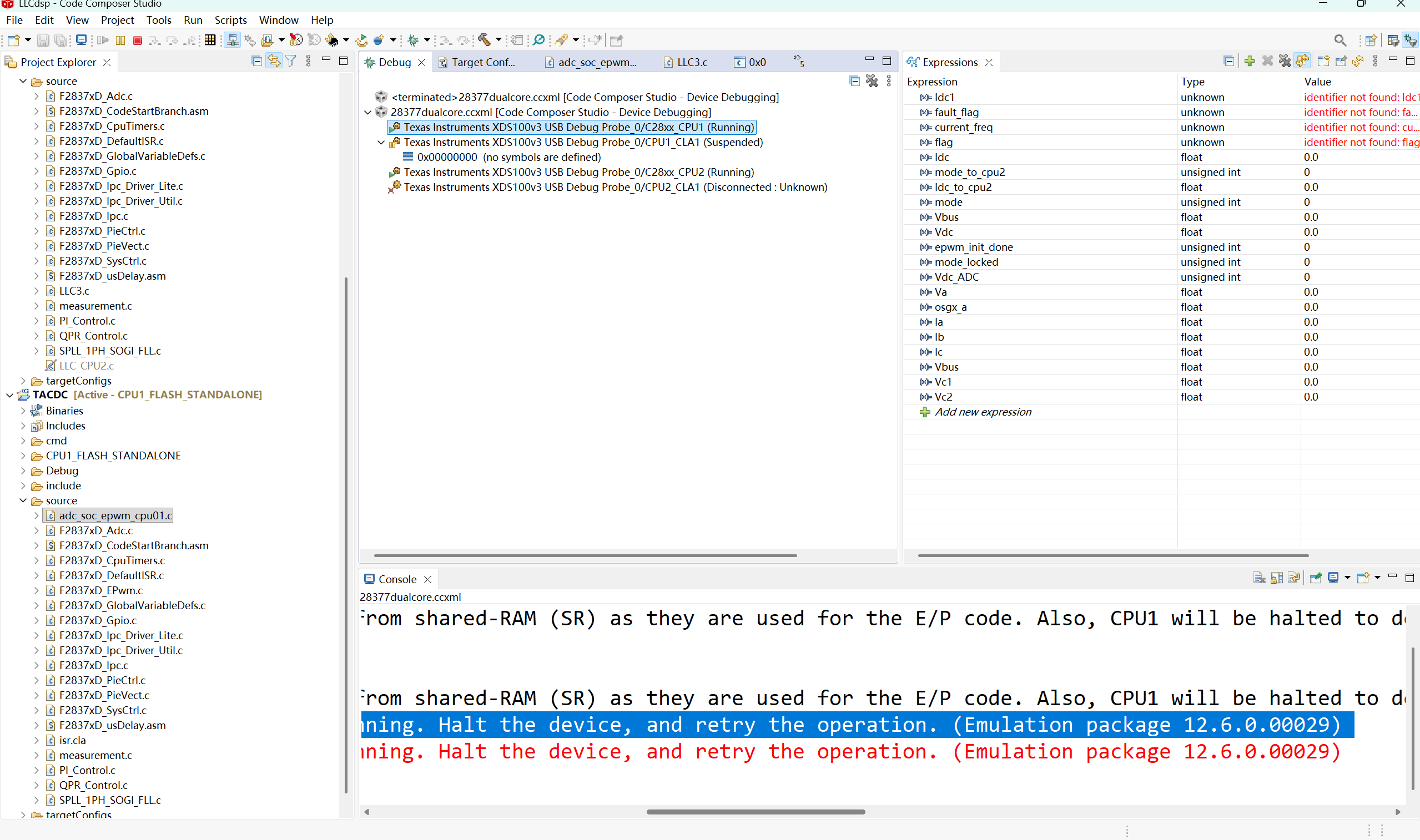

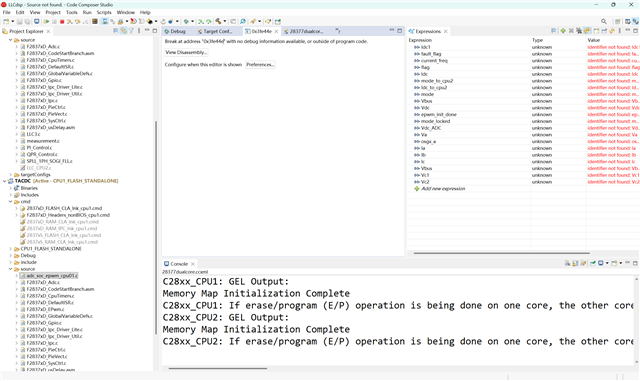

而如果按双核烧写的流程先connect cpu1,cla1,cpu2,然后分别load cpu1,cpu2的.out文件,对cpu1cla load symbol,再依次run cpu1,cla,cpu2,发现无法进到cla中断里(通过观察cla中的变量osgx_a)并且cpu1似乎也没有在进程中因为观察变量没有实时刷新,run cpu1会显示跳转:Break at address "0x3fe44e" with no debug information available, or outside of program code.

run cla会显示跳转:Break at address "0x0" with no debug information available, or outside of program code.

报错: Can't Run Target CPU: (Error -2060 @ 0x0) Requested operation cannot be done while device is running. Halt the device, and retry the operation. (Emulation package 12.6.0.00029) 如图

2837xD_FLASH_CLA_lnk_cpu1.cmd:

// The user must define CLA_C in the project linker settings if using the

// CLA C compiler

// Project Properties -> C2000 Linker -> Advanced Options -> Command File

// Preprocessing -> --define

#ifdef CLA_C

// Define a size for the CLA scratchpad area that will be used

// by the CLA compiler for local symbols and temps

// Also force references to the special symbols that mark the

// scratchpad are.

CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

#endif //CLA_C

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to SARAM" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x000122, length = 0x0002DE

RAMD0 : origin = 0x00B000, length = 0x000800

RAMLS4 : origin = 0x00A000, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x000800

RAMGS14 : origin = 0x01A000, length = 0x001000

RAMGS15 : origin = 0x01B000, length = 0x001000

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

FLASHA : origin = 0x080002, length = 0x001FFE /* on-chip Flash */

FLASHB : origin = 0x082000, length = 0x002000 /* on-chip Flash */

FLASHC : origin = 0x084000, length = 0x002000 /* on-chip Flash */

FLASHD : origin = 0x086000, length = 0x002000 /* on-chip Flash */

FLASHE : origin = 0x088000, length = 0x008000 /* on-chip Flash */

FLASHF : origin = 0x090000, length = 0x008000 /* on-chip Flash */

FLASHG : origin = 0x098000, length = 0x008000 /* on-chip Flash */

FLASHH : origin = 0x0A0000, length = 0x008000 /* on-chip Flash */

FLASHI : origin = 0x0A8000, length = 0x008000 /* on-chip Flash */

FLASHJ : origin = 0x0B0000, length = 0x008000 /* on-chip Flash */

FLASHK : origin = 0x0B8000, length = 0x002000 /* on-chip Flash */

FLASHL : origin = 0x0BA000, length = 0x002000 /* on-chip Flash */

FLASHM : origin = 0x0BC000, length = 0x002000 /* on-chip Flash */

FLASHN : origin = 0x0BE000, length = 0x002000 /* on-chip Flash */

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x000120 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAMLS0 : origin = 0x008000, length = 0x000800

RAMLS1 : origin = 0x008800, length = 0x000800

RAMLS2 : origin = 0x009000, length = 0x000800

RAMLS3 : origin = 0x009800, length = 0x000800

RAMGS0 : origin = 0x00C000, length = 0x001000

RAMGS1 : origin = 0x00D000, length = 0x001000

RAMGS2 : origin = 0x00E000, length = 0x001000

RAMGS3 : origin = 0x00F000, length = 0x001000

RAMGS4 : origin = 0x010000, length = 0x001000

RAMGS5 : origin = 0x011000, length = 0x001000

RAMGS6 : origin = 0x012000, length = 0x001000

RAMGS7 : origin = 0x013000, length = 0x001000

RAMGS8 : origin = 0x014000, length = 0x001000

RAMGS9 : origin = 0x015000, length = 0x001000

RAMGS10 : origin = 0x016000, length = 0x001000

RAMGS11 : origin = 0x017000, length = 0x001000

RAMGS12 : origin = 0x018000, length = 0x001000

RAMGS13 : origin = 0x019000, length = 0x001000

CPU2TOCPU1RAM : origin = 0x03F800, length = 0x000400

CPU1TOCPU2RAM : origin = 0x03FC00, length = 0x000400

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB PAGE = 0, ALIGN(4)

.pinit : > FLASHB, PAGE = 0, ALIGN(4)

.text : >> FLASHB |FLASHC|FLASHE PAGE = 0, ALIGN(4)

codestart : > BEGIN PAGE = 0, ALIGN(4)

//ramfuncs : LOAD = FLASHD,

//RUN = RAMLS4,

// LOAD_START(_RamfuncsLoadStart),

// LOAD_SIZE(_RamfuncsLoadSize),

// LOAD_END(_RamfuncsLoadEnd),

// RUN_START(_RamfuncsRunStart),

// RUN_SIZE(_RamfuncsRunSize),

// RUN_END(_RamfuncsRunEnd),

// PAGE = 0, ALIGN(4)

/* Allocate uninitalized data sections: */

.stack : > RAMM1 PAGE = 1

.ebss : > RAMLS2 PAGE = 1

.esysmem : > RAMLS2 PAGE = 1

/* Initalized sections go in Flash */

.econst : > FLASHB PAGE = 0, ALIGN(4)

.switch : > FLASHB PAGE = 0, ALIGN(4)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

Filter_RegsFile : > RAMGS0, PAGE = 1

/* CLA specific sections */

Cla1Prog : LOAD = FLASHD,

RUN = RAMLS5,

LOAD_START(_Cla1funcsLoadStart),

LOAD_END(_Cla1funcsLoadEnd),

RUN_START(_Cla1funcsRunStart),

LOAD_SIZE(_Cla1funcsLoadSize),

PAGE = 0, ALIGN(4)

CLADataLS0 : > RAMLS0, PAGE=1

CLADataLS1 : > RAMLS1, PAGE=1

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

.TI.ramfunc : {} LOAD = FLASHD,

RUN = RAMLS4,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

/* The following section definition are for SDFM examples */

Filter1_RegsFile : > RAMGS1, PAGE = 1, fill=0x1111

Filter2_RegsFile : > RAMGS2, PAGE = 1, fill=0x2222

Filter3_RegsFile : > RAMGS3, PAGE = 1, fill=0x3333

Filter4_RegsFile : > RAMGS4, PAGE = 1, fill=0x4444

Difference_RegsFile : > RAMGS5, PAGE = 1, fill=0x3333

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM PAGE = 1

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM PAGE = 1

IPC_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

GROUP : > CPU1TOCPU2RAM, PAGE = 1

{

PUTBUFFER

PUTWRITEIDX

GETREADIDX

}

GROUP : > CPU2TOCPU1RAM, PAGE = 1

{

GETBUFFER : TYPE = DSECT

GETWRITEIDX : TYPE = DSECT

PUTREADIDX : TYPE = DSECT

}

#ifdef CLA_C

/* CLA C compiler sections */

//

// Must be allocated to memory the CLA has write access to

//

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > RAMLS1, PAGE = 1

.scratchpad : > RAMLS1, PAGE = 1

.bss_cla : > RAMLS1, PAGE = 1

.const_cla : LOAD = FLASHB,

RUN = RAMLS1,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

PAGE = 1

#endif //CLA_C

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

想知道是烧写方式有问题还是cmd的内存分配有问题或是其他问题