Other Parts Discussed in Thread: C2000WARE

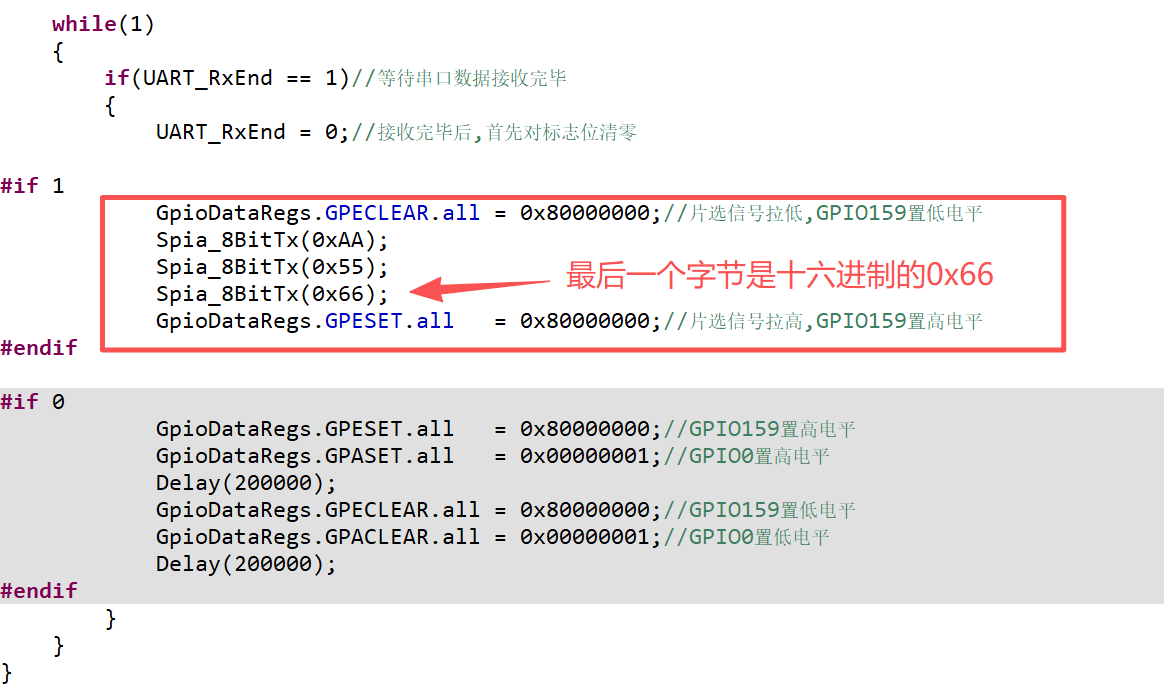

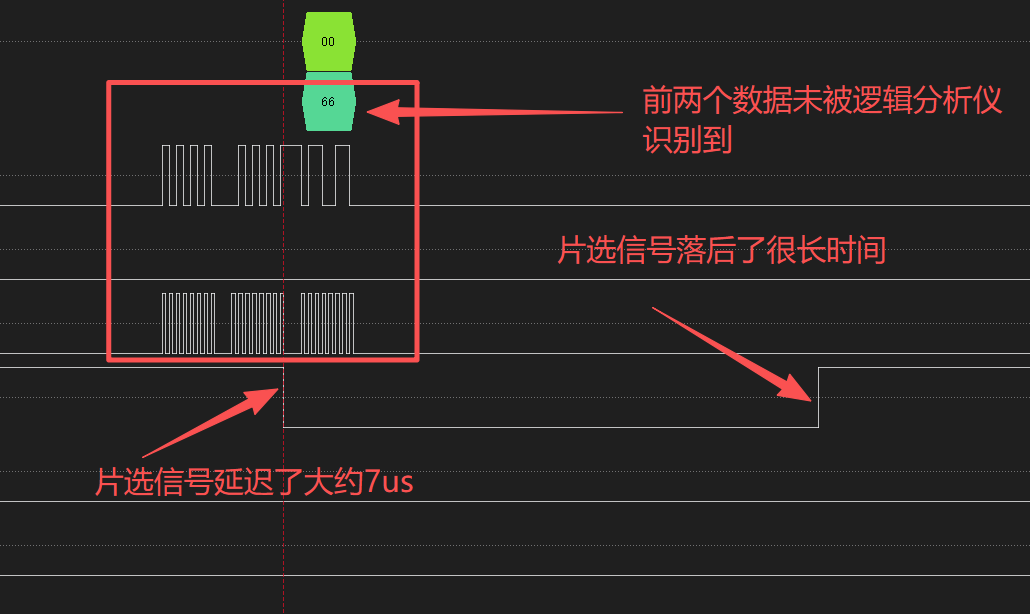

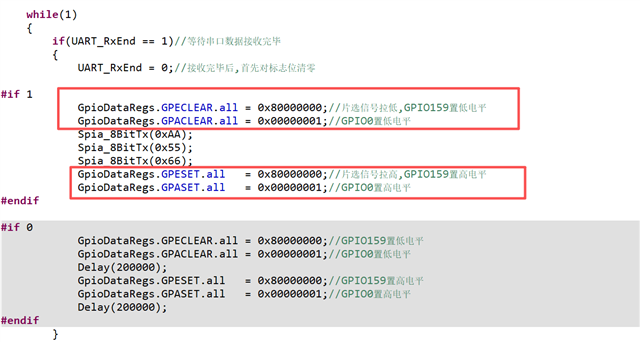

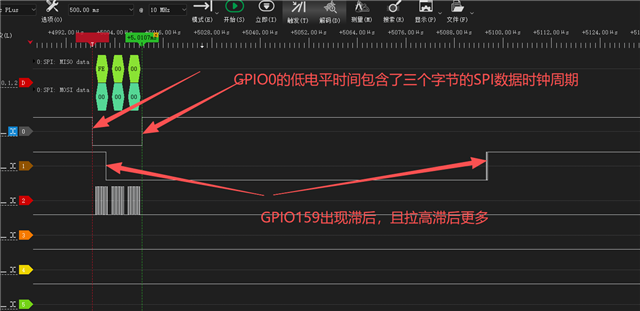

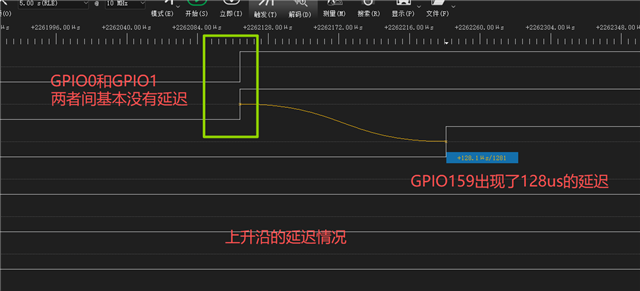

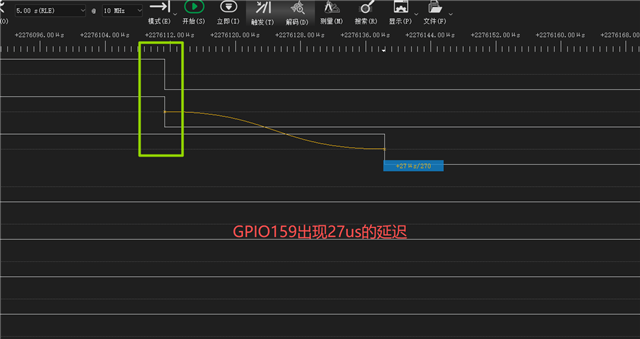

如题,电路设计中将GPIO159设置外部SPI接口的EEPROM器件的片选端,由软件手动控制该IO口,读写存储器期间,发现片选端已事先手动拉低到低电平,但逻辑分析仪扫描SPI接口所有信号,发现时间上是先出现的SPI的时钟和数据信号,片选信号居然延迟了一段时间才被实际拉低;不仅如此,在SPI接口数据发送完毕后,代码上是立刻将片选信号再次拉高,结果发现GPIO159在延迟了很长时间后才真正置为了高电平,代码和逻辑分析仪截图如下:

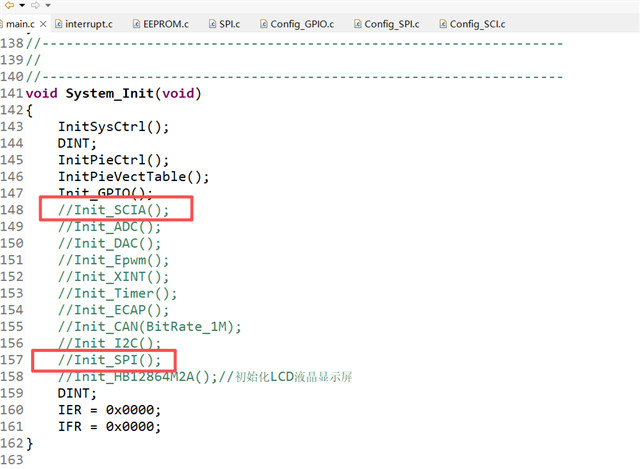

串口和SPI的初始化都关闭了

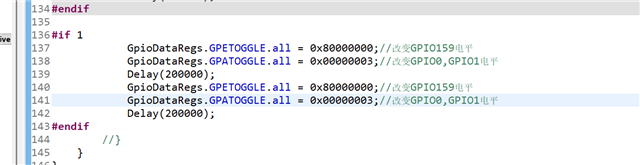

串口和SPI的初始化都关闭了 while循环里面只做两个IO口的电平翻转

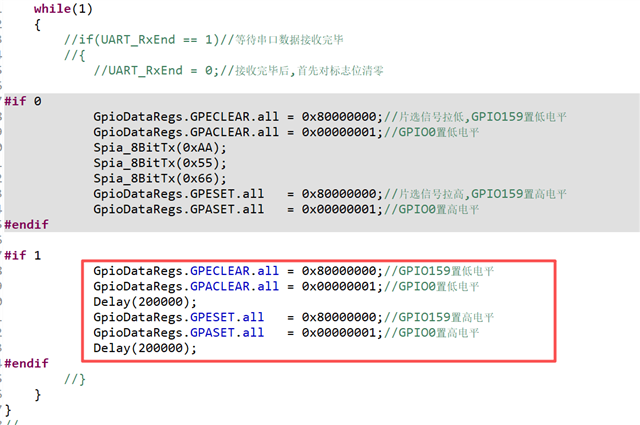

while循环里面只做两个IO口的电平翻转

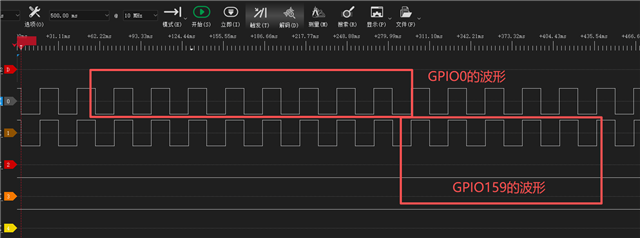

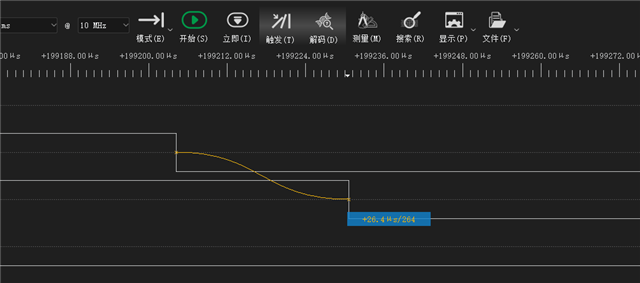

电平由高到低期间,GPIO159比GPIO0延迟大约26us

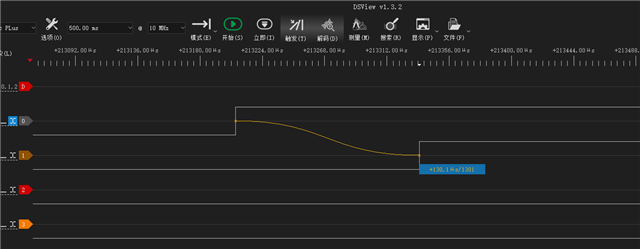

电平由高到低期间,GPIO159比GPIO0延迟大约26us 电平由低到高期间,GPIO159比GPIO0延迟大约130us

电平由低到高期间,GPIO159比GPIO0延迟大约130us 这是代码截图

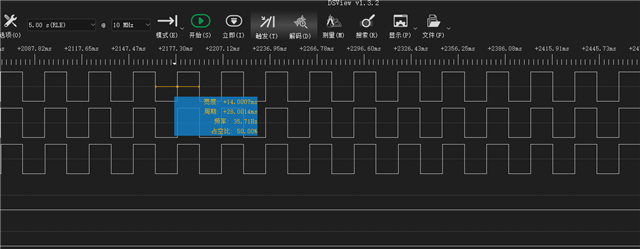

这是代码截图 逻辑分析仪截图,从上到下分别是GPIO0 GPIO1 GPIO159

逻辑分析仪截图,从上到下分别是GPIO0 GPIO1 GPIO159

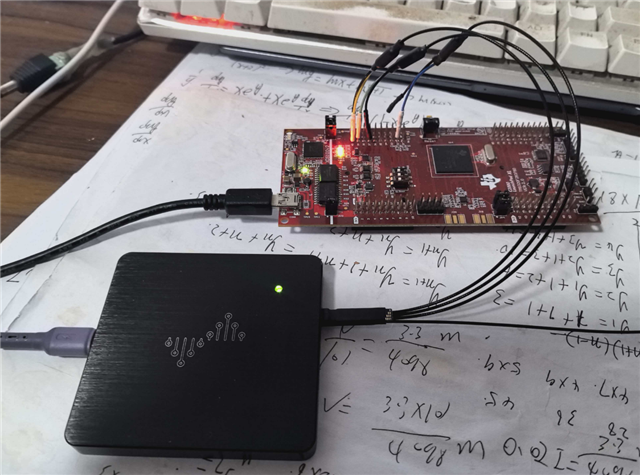

LaunchPad XL板子就只接了个逻辑分析仪,所以排除了外部器件影响GPIO159的可能性了

LaunchPad XL板子就只接了个逻辑分析仪,所以排除了外部器件影响GPIO159的可能性了