Part Number: TMS320F280039

Other Parts Discussed in Thread: PMP41081

TI专家您好!

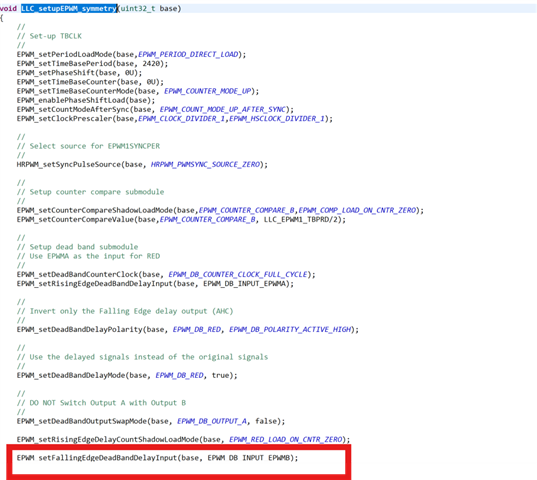

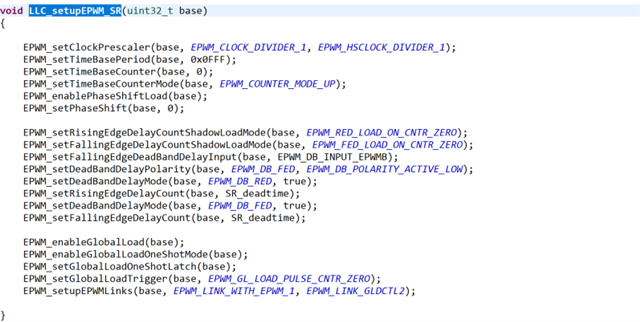

最近在学习PMP4108混合迟滞控制LLC,关于CLB的相关配置有如下疑问:

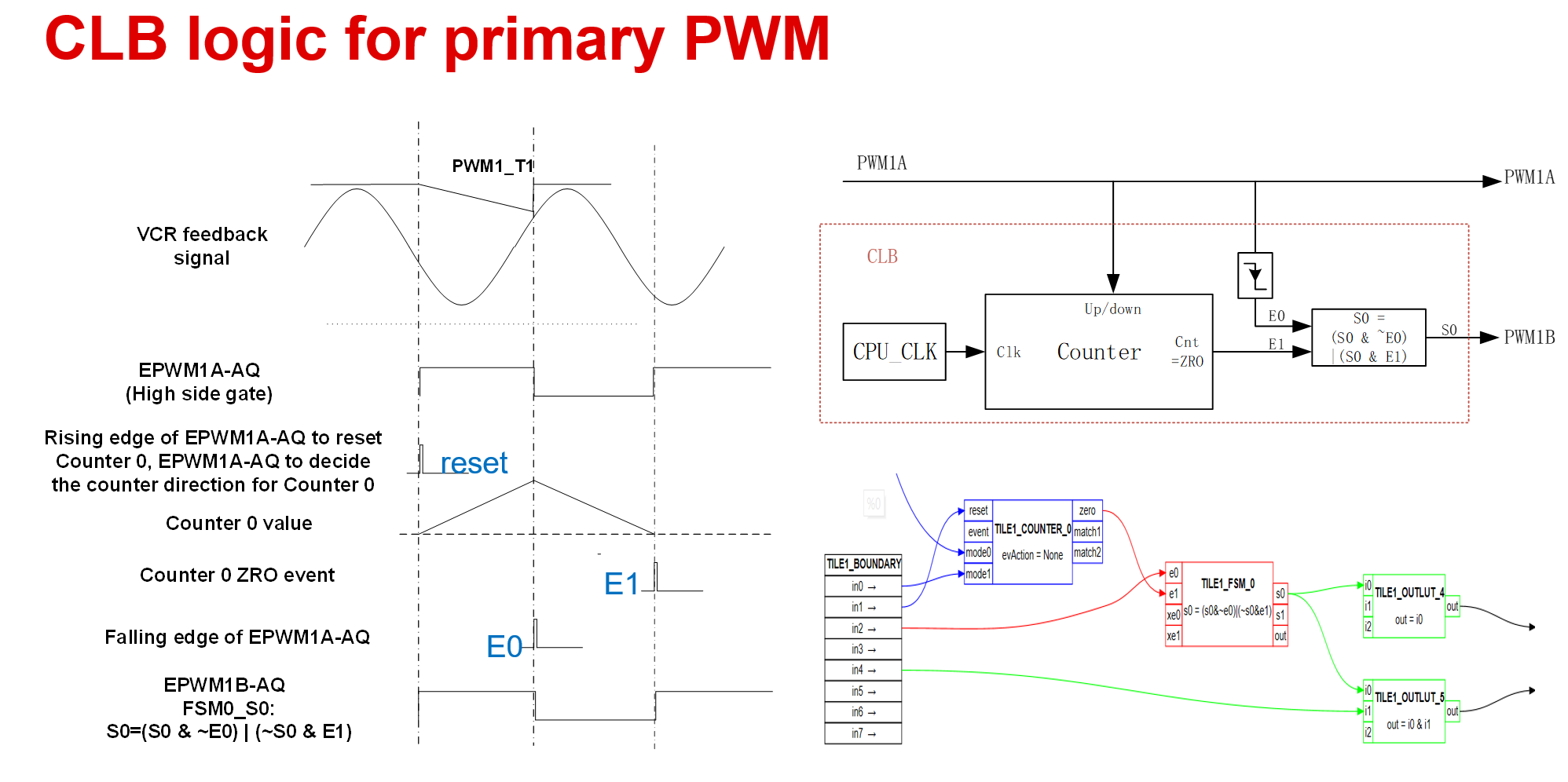

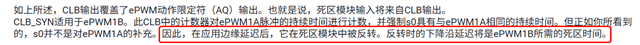

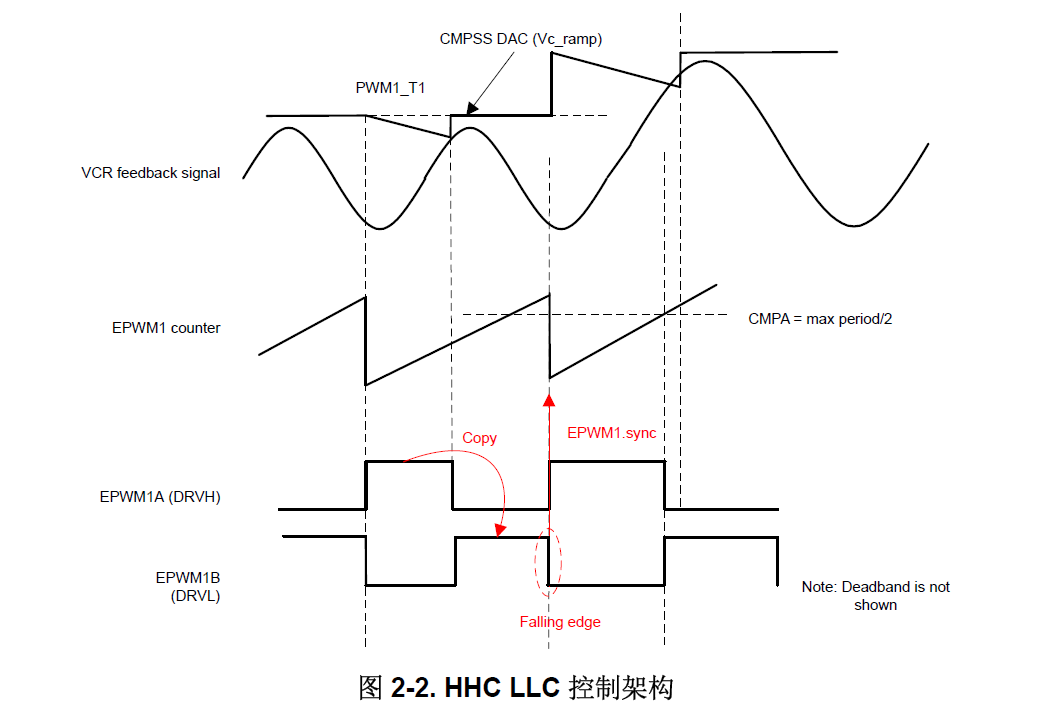

在初级侧CLB用于将EPWM1A的输出复制到EPWM1B的输出,EPWM1A和EPWM1B是互补波形吧?如下图底部的波形所示:

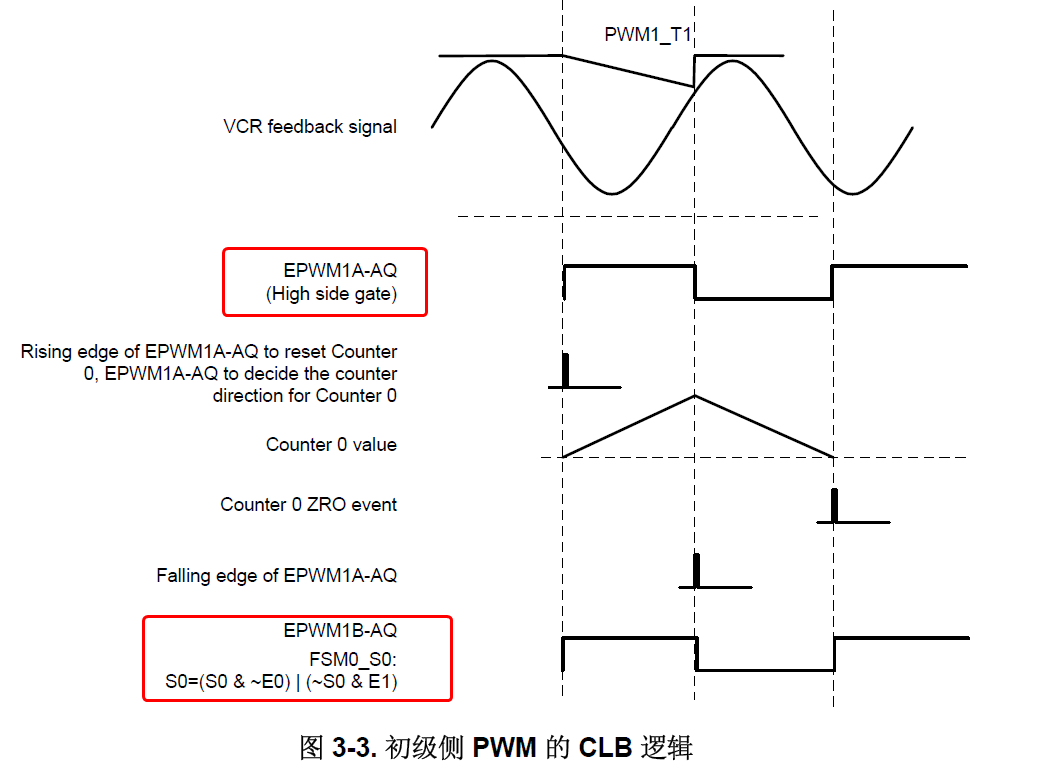

可为什么在CLB的配置中却变成了如下的波形?看起来两路输出也不是互补波形了:

根据你们提供的文档,当计数器Counter 0 ZRO event事件作为有限状态机的e1输入,结合e0(EPWM1A的下降沿)共同决定s0的输出,最终控制TILE1_OUTLUT_5,如下图所示,就是不明白这些波形是怎么回事,s0的输出难道和EPWM1B输出不同吗?麻烦专家们帮忙解释下,谢谢了!