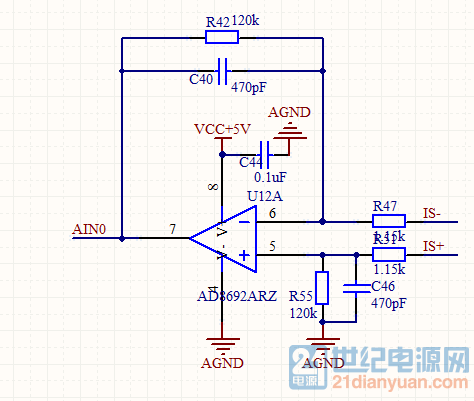

我通过采样电阻采集DCDC电路的输出电流,然后经差分电路转换成一定的电压,送进0采样通道。现在是单电流闭环一直闭不上,我想输出电流稳定为6A,可是不论怎么调kp ki参数,输出电流都是从4A左右,大概经过3分钟左右才能稳定到6A。当只有比例部分时,一上电输出电流也是从4A左右,慢慢增加,当然达不到6A。我现在就怀疑是dsp采集的电流信号不准备。我给0采样通道一个固定值,比如1.2V,用公式计算的数字量为1489,但是通过CCS观察窗口看到0结果寄存器里的数字大概为1592左右,有一定的偏差。您感觉这个误差是导致单电流闭环出现上述情况的原因吗?