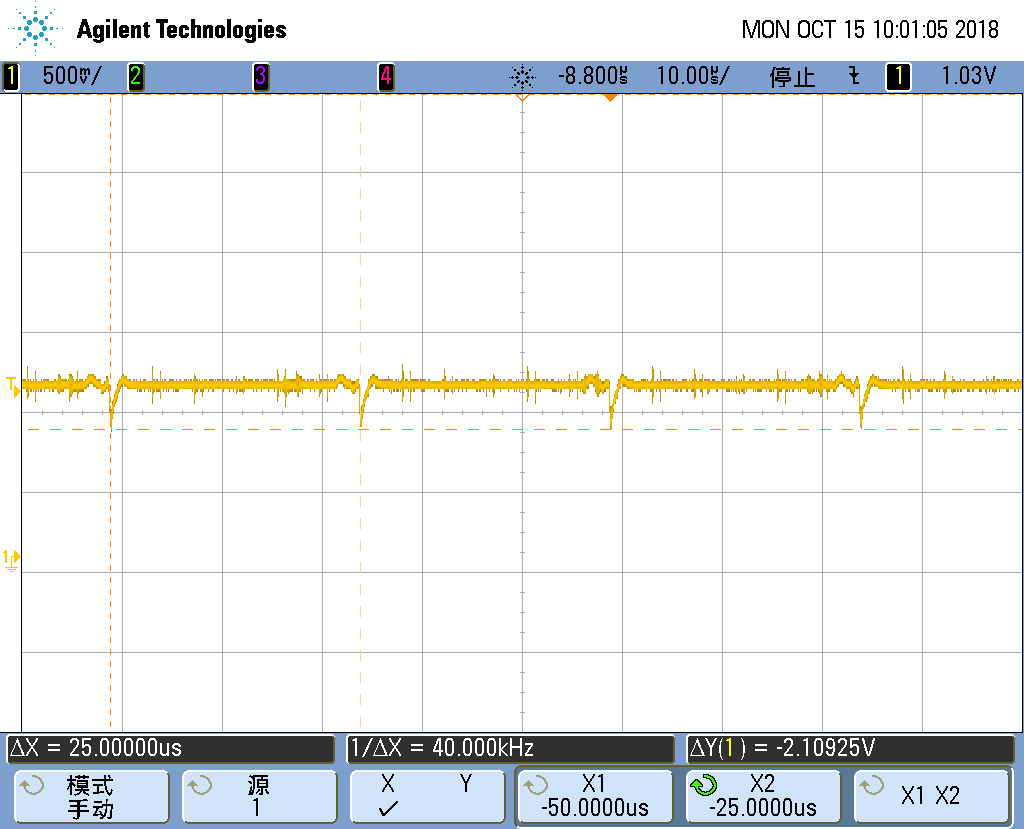

我使用40K的采样频率去采样一电压。结果发现每次触发采样,到DSP的ADC引脚上的电压就会被拉低一个坑,如下图1所示。

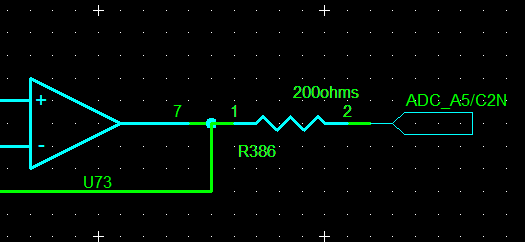

采样调理电路输出与ADC引脚中间加了个200欧的限流电阻,如图2所示的R386。用示波器量得R386的1引脚的电压(也就是调理电路输出电压)是正常的1.2V。

但用示波器量得的R386的2引脚电压(也就是DSP的ADC引脚)只有1V,并且每次触发采样,电压都会被拉低一个坑。

所以可以判断这个现象跟调理电路设计应该没太大关系,应该跟DSP的ADC引脚内部电路有关系。想请问一下这是由什么原因照成的?