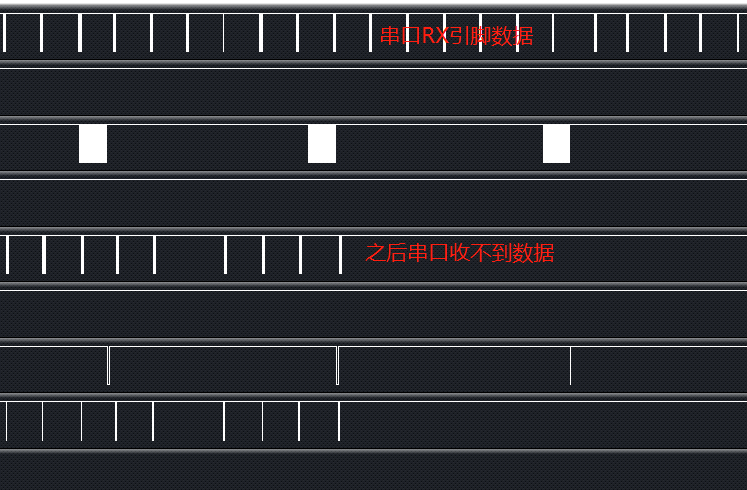

串口通信帧数据频率 100hz

开机时正常 过一段时间后收不到数据 有时候几秒钟 有时候几分钟 如果把数据不连续发送就能正常工作 请问如何解决

volatile unsigned long recv_uart_b_interrupt_data = 0;

volatile unsigned long load_uart_b_interrupt_data = 0;

volatile unsigned char recv_uart_b_tmp_data[ RECV_SIC_SINS_DATA_LENGTH + 2 ];

void init_scib_gpio()

{

// SCI-RX

GPIO_SetupPinMux(19, GPIO_MUX_CPU1,2);

GPIO_SetupPinOptions(19, GPIO_INPUT, GPIO_PUSHPULL);

// SCI-TX

GPIO_SetupPinMux(18, GPIO_MUX_CPU1, 2);

GPIO_SetupPinOptions(18, GPIO_OUTPUT, GPIO_ASYNC);

}

void scib_fifo_init()

{

ScibRegs.SCICCR.all = 0x0007; // 1 stop bit, No loopback

// No parity,8 char bits,

// async mode, idle-line protocol

ScibRegs.SCICTL1.all = 0x0003; // enable TX, RX, internal SCICLK,

// Disable RX ERR, SLEEP, TXWAKE

ScibRegs.SCIHBAUD = 0x00;

ScibRegs.SCILBAUD = 0x06;

ScibRegs.SCIFFTX.bit.SCIFFENA = 1;//使能FIFO

ScibRegs.SCIFFTX.bit.SCIRST = 1;//继续执行功能

ScibRegs.SCIFFTX.bit.TXFFIENA =1;//使能发送FIFO中断

ScibRegs.SCIFFTX.bit.TXFFIL = 0x01;//12级FIFO使能

// ScibRegs.SCIFFTX.bit.TXFFINTCLR = 1; // 开始发送数据

ScibRegs.SCIFFTX.bit.TXFIFOXRESET = 0;

ScibRegs.SCIFFRX.bit.RXFFOVRCLR = 1;

ScibRegs.SCIFFRX.bit.RXFFINTCLR = 1;

ScibRegs.SCIFFRX.bit.RXFIFORESET = 0;

ScibRegs.SCIFFRX.bit.RXFFIENA = 1;

ScibRegs.SCIFFRX.bit.RXFFIL = 0x01;

ScibRegs.SCIFFCT.all = 0x00;

ScibRegs.SCICTL1.bit.SWRESET = 1;//Relinquish SCI from Reset

ScibRegs.SCIFFTX.bit.TXFIFOXRESET = 1;

ScibRegs.SCIFFRX.bit.RXFIFORESET = 1;

}

接收中断函数

interrupt void scibRxIsr( void )

{

unsigned char recv_data = ( ScibRegs.SCIRXBUF.all ) & 0x00FF;

// 保存数据

//GpioDataRegs.GPATOGGLE.bit.GPIO26 = 1;

recv_uart_b_tmp_data[ recv_uart_b_interrupt_data ] = recv_data;

++recv_uart_b_interrupt_data;

recv_uart_b_interrupt_data %= RECV_SIC_SINS_DATA_LENGTH;

ScibRegs.SCIFFRX.bit.RXFFOVRCLR = 1;

ScibRegs.SCIFFRX.bit.RXFFINTCLR = 1;

//PieCtrlRegs.PIEACK.bit.ACK9 = 1; //当中断处理完成后,需要用程序将该组ACK置1,否则会出现该组某一中断一直出现的情况

PieCtrlRegs.PIEACK.all |= PIEACK_GROUP9;

}

串口异常后的寄存器值

ScibRegs struct SCI_REGS {...} 0x00007210@Data

SCICCR union SCICCR_REG {...} 0x00007210@Data

all unsigned int 7 0x00007210@Data

bit struct SCICCR_BITS {...} 0x00007210@Data

SCICHAR unsigned int : 3 7 0x00007210@Data bit 0-2

ADDRIDLE_MODE unsigned int : 1 0 0x00007210@Data bit 3

LOOPBKENA unsigned int : 1 0 0x00007210@Data bit 4

PARITYENA unsigned int : 1 0 0x00007210@Data bit 5

PARITY unsigned int : 1 0 0x00007210@Data bit 6

STOPBITS unsigned int : 1 0 0x00007210@Data bit 7

rsvd1 unsigned int : 8 0 0x00007210@Data bit 8-15

SCICTL1 union SCICTL1_REG {...} 0x00007211@Data

all unsigned int 35 0x00007211@Data

bit struct SCICTL1_BITS {...} 0x00007211@Data

RXENA unsigned int : 1 1 0x00007211@Data bit 0

TXENA unsigned int : 1 1 0x00007211@Data bit 1

SLEEP unsigned int : 1 0 0x00007211@Data bit 2

TXWAKE unsigned int : 1 0 0x00007211@Data bit 3

rsvd1 unsigned int : 1 0 0x00007211@Data bit 4

SWRESET unsigned int : 1 1 0x00007211@Data bit 5

RXERRINTENA unsigned int : 1 0 0x00007211@Data bit 6

rsvd2 unsigned int : 9 0 0x00007211@Data bit 7-15

SCIHBAUD unsigned int 0 0x00007212@Data

SCILBAUD unsigned int 6 0x00007213@Data

SCICTL2 union SCICTL2_REG {...} 0x00007214@Data

all unsigned int 192 0x00007214@Data

bit struct SCICTL2_BITS {...} 0x00007214@Data

TXINTENA unsigned int : 1 0 0x00007214@Data bit 0

RXBKINTENA unsigned int : 1 0 0x00007214@Data bit 1

rsvd1 unsigned int : 4 0 0x00007214@Data bit 2-5

TXEMPTY unsigned int : 1 1 0x00007214@Data bit 6

TXRDY unsigned int : 1 1 0x00007214@Data bit 7

rsvd2 unsigned int : 8 0 0x00007214@Data bit 8-15

SCIRXST union SCIRXST_REG {...} 0x00007215@Data

all unsigned int 178 0x00007215@Data

bit struct SCIRXST_BITS {...} 0x00007215@Data

rsvd1 unsigned int : 1 0 0x00007215@Data bit 0

RXWAKE unsigned int : 1 1 0x00007215@Data bit 1

PE unsigned int : 1 0 0x00007215@Data bit 2

OE unsigned int : 1 0 0x00007215@Data bit 3

FE unsigned int : 1 1 0x00007215@Data bit 4

BRKDT unsigned int : 1 1 0x00007215@Data bit 5

RXRDY unsigned int : 1 0 0x00007215@Data bit 6

RXERROR unsigned int : 1 1 0x00007215@Data bit 7

rsvd2 unsigned int : 8 0 0x00007215@Data bit 8-15

SCIRXEMU unsigned int 35 0x00007216@Data

SCIRXBUF union SCIRXBUF_REG {...} 0x00007217@Data

all unsigned int 63 0x00007217@Data

bit struct SCIRXBUF_BITS {...} 0x00007217@Data

RXDT unsigned int : 8 63 0x00007217@Data bit 0-7

rsvd1 unsigned int : 6 0 0x00007217@Data bit 8-13

SCIFFPE unsigned int : 1 0 0x00007217@Data bit 14

SCIFFFE unsigned int : 1 0 0x00007217@Data bit 15

rsvd1 unsigned int 0 0x00007218@Data

SCITXBUF unsigned int 136 0x00007219@Data

SCIFFTX union SCIFFTX_REG {...} 0x0000721A@Data

all unsigned int 57505 0x0000721A@Data

bit struct SCIFFTX_BITS {...} 0x0000721A@Data

TXFFIL unsigned int : 5 1 0x0000721A@Data bit 0-4

TXFFIENA unsigned int : 1 1 0x0000721A@Data bit 5

TXFFINTCLR unsigned int : 1 0 0x0000721A@Data bit 6

TXFFINT unsigned int : 1 1 0x0000721A@Data bit 7

TXFFST unsigned int : 5 0 0x0000721A@Data bit 8-12

TXFIFOXRESET unsigned int : 1 1 0x0000721A@Data bit 13

SCIFFENA unsigned int : 1 1 0x0000721A@Data bit 14

SCIRST unsigned int : 1 1 0x0000721A@Data bit 15

SCIFFRX union SCIFFRX_REG {...} 0x0000721B@Data

all unsigned int 8225 0x0000721B@Data

bit struct SCIFFRX_BITS {...} 0x0000721B@Data

RXFFIL unsigned int : 5 1 0x0000721B@Data bit 0-4

RXFFIENA unsigned int : 1 1 0x0000721B@Data bit 5

RXFFINTCLR unsigned int : 1 0 0x0000721B@Data bit 6

RXFFINT unsigned int : 1 0 0x0000721B@Data bit 7

RXFFST unsigned int : 5 0 0x0000721B@Data bit 8-12

RXFIFORESET unsigned int : 1 1 0x0000721B@Data bit 13

RXFFOVRCLR unsigned int : 1 0 0x0000721B@Data bit 14

RXFFOVF unsigned int : 1 0 0x0000721B@Data bit 15

SCIFFCT union SCIFFCT_REG {...} 0x0000721C@Data

all unsigned int 0 0x0000721C@Data

bit struct SCIFFCT_BITS {...} 0x0000721C@Data

FFTXDLY unsigned int : 8 0 0x0000721C@Data bit 0-7

rsvd1 unsigned int : 5 0 0x0000721C@Data bit 8-12

CDC unsigned int : 1 0 0x0000721C@Data bit 13

ABDCLR unsigned int : 1 0 0x0000721C@Data bit 14

ABD unsigned int : 1 0 0x0000721C@Data bit 15

rsvd2 unsigned int 0 0x0000721D@Data

rsvd3 unsigned int 0 0x0000721E@Data

SCIPRI union SCIPRI_REG {...} 0x0000721F@Data

all unsigned int 0 0x0000721F@Data

bit struct SCIPRI_BITS {...} 0x0000721F@Data

rsvd1 unsigned int : 3 0 0x0000721F@Data bit 0-2

FREE unsigned int : 1 0 0x0000721F@Data bit 3

SOFT unsigned int : 1 0 0x0000721F@Data bit 4

rsvd2 unsigned int : 3 0 0x0000721F@Data bit 5-7

rsvd3 unsigned int : 8 0 0x0000721F@Data bit 8-15

连续发生数据

数据间隔发送