AD采样通道顺序不同采样结果不同 这两段程序配置完全相同,只是顺序不同

用第一个程序采样正常,屏蔽第一段用第二个 采样 有偏差。偏差达到40左右

请问这是什么原因??先谢谢了

程序如下:

/*AdcRegs.ADCSOC0CTL.bit.CHSEL = 6; //set SOC0 电感电流 ADCINA6

AdcRegs.ADCSOC1CTL.bit.CHSEL = 9; //set SOC1 超容侧电压 ADCINB1

AdcRegs.ADCSOC2CTL.bit.CHSEL = 1; //set SOC2 输出侧电压 ADCINA1

AdcRegs.ADCSOC3CTL.bit.CHSEL = 15; //set SOC3 温度 ADCINB7

AdcRegs.ADCSOC4CTL.bit.CHSEL = 11; //set SOC4 二极管前端电压 ADCINB3

AdcRegs.ADCSOC5CTL.bit.CHSEL = 4; //set SOC5 电感电流I1 ADCINA4

AdcRegs.ADCSOC6CTL.bit.CHSEL = 7; //set SOC6 电感电流I2 ADCINA7

AdcRegs.ADCSOC7CTL.bit.CHSEL = 3; //set SOC7 电感电流I3 ADCINA3

AdcRegs.ADCSOC8CTL.bit.CHSEL = 0; //1.65V采样

*/

AdcRegs.ADCSOC0CTL.bit.CHSEL = 6; //set 电感电流 ADCINA6

AdcRegs.ADCSOC1CTL.bit.CHSEL = 4; //set 电感电流 ADCINA4

AdcRegs.ADCSOC2CTL.bit.CHSEL = 7; //set 电感电流 ADCINA7

AdcRegs.ADCSOC3CTL.bit.CHSEL = 3; //set 电感电流 ADCINA3

AdcRegs.ADCSOC4CTL.bit.CHSEL = 1; //set 输出侧电压 ADCINA1

AdcRegs.ADCSOC5CTL.bit.CHSEL = 0; //set 1.65V ADCINA0

AdcRegs.ADCSOC6CTL.bit.CHSEL = 9; //set 超容侧电压 ADCINB1

AdcRegs.ADCSOC7CTL.bit.CHSEL = 11; //set 二极管前端电压 ADCINB3

AdcRegs.ADCSOC8CTL.bit.CHSEL = 15; //set 温度 ADCINB7

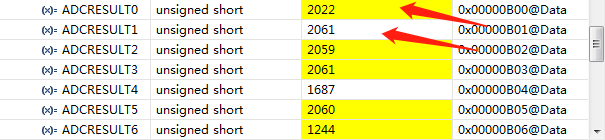

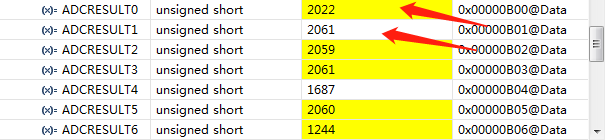

采样结果: