各位技术仁兄:

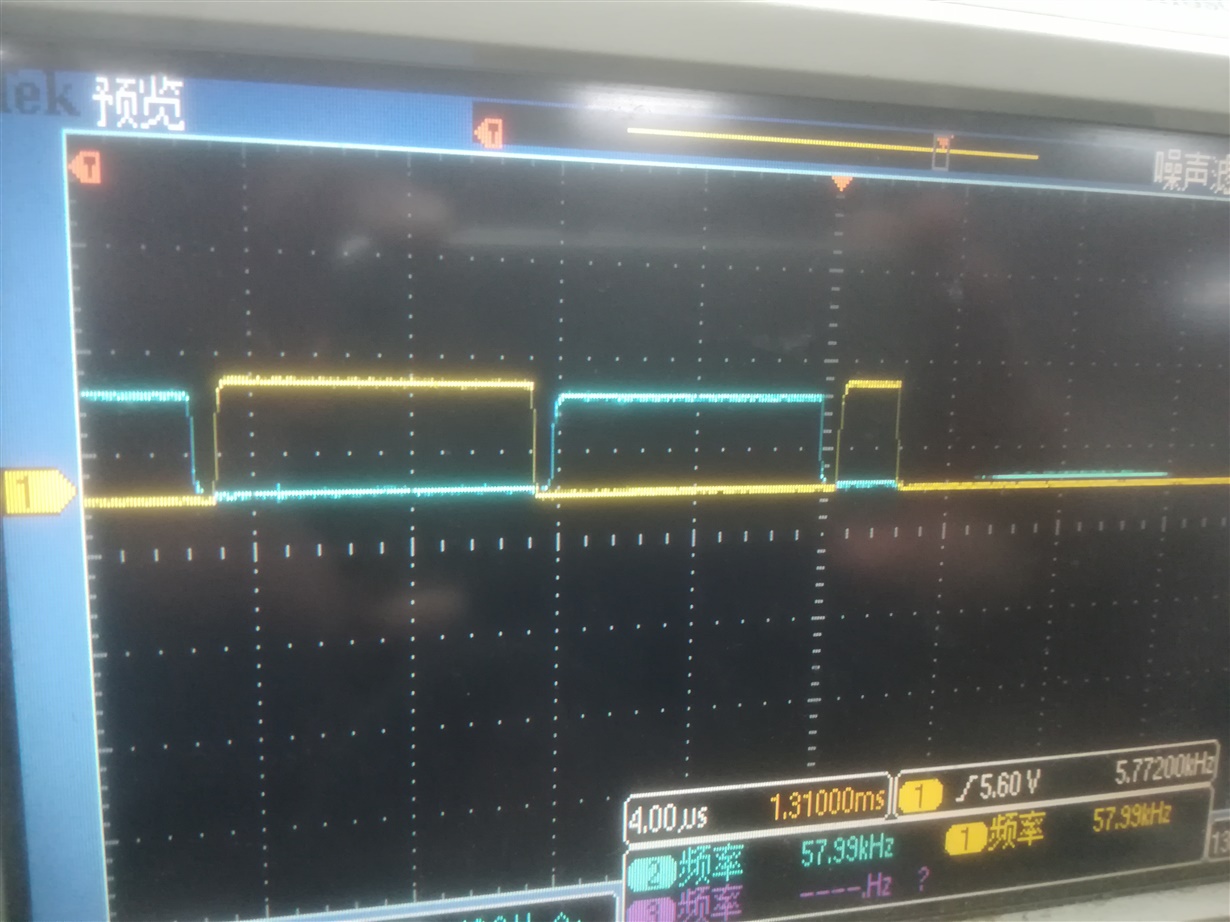

本人在使用28069做项目时,需要输出一路对称的PWM信号控制半桥,PWM频率为50KHZ,配置输出2ms PWM信号后,使用软件延时2ms,Delay2ms后控制把PWM信号强制关闭,如

EPwm1Regs.TZFRC.bit.OST = 1; //强制TZ模式清除PWM---stop

EPwm2Regs.TZFRC.bit.OST = 1; //强制TZ模式清除PWM---stop

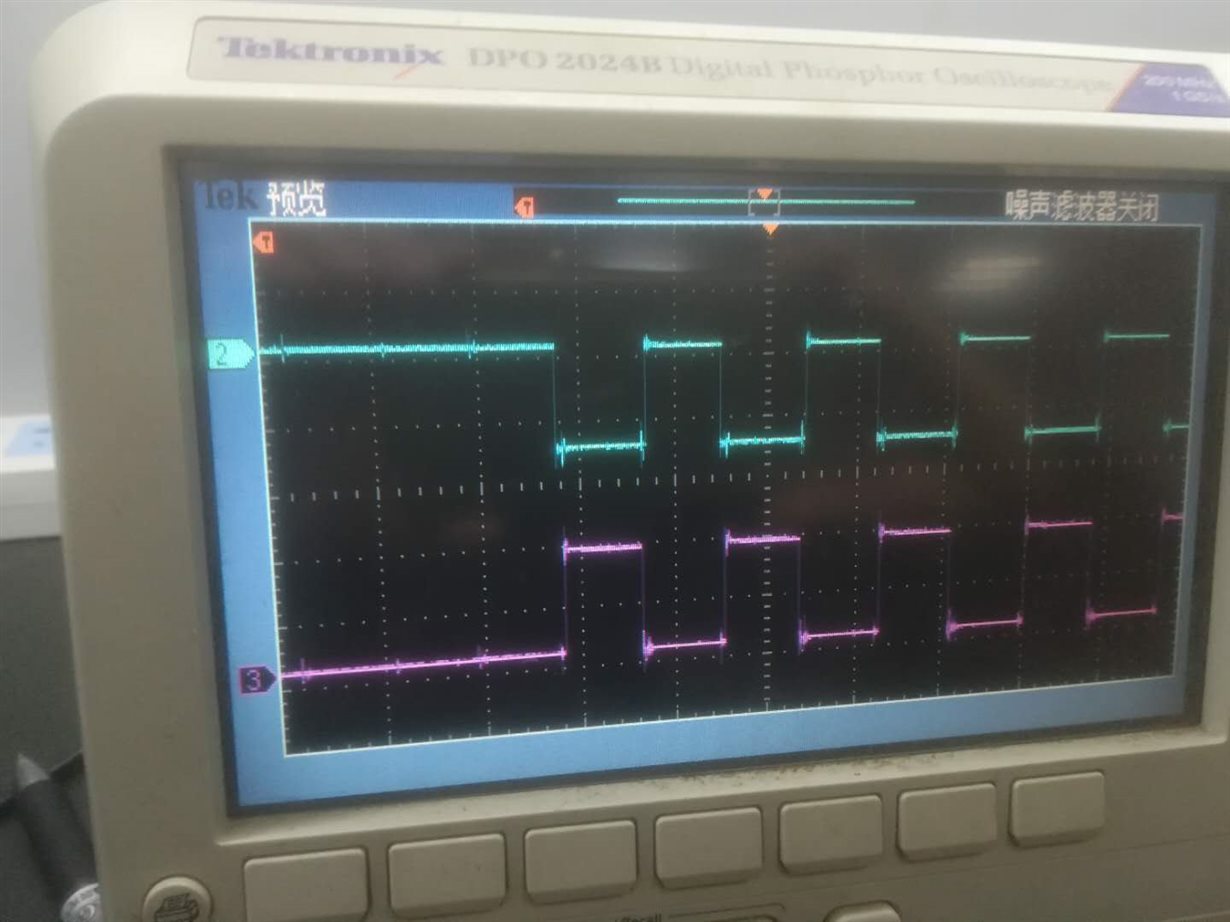

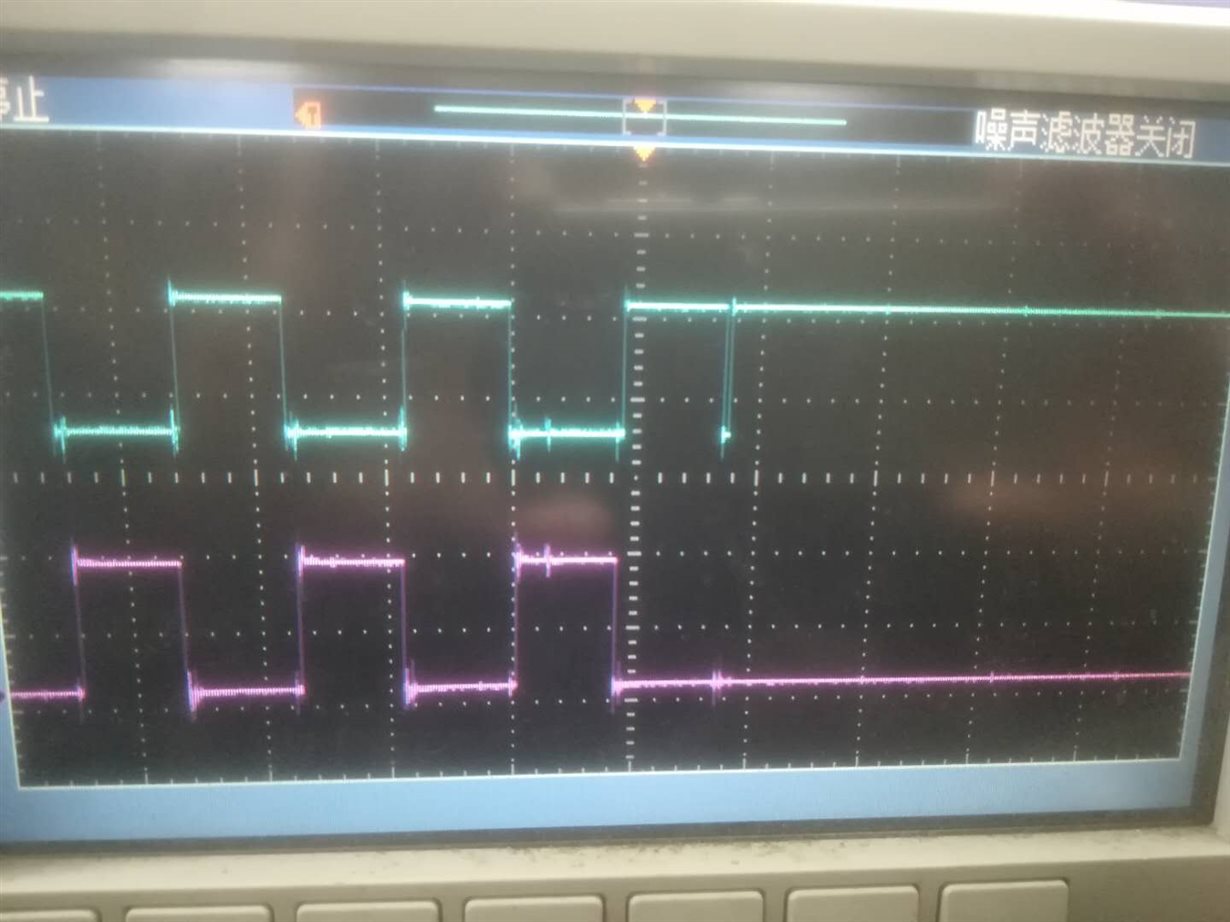

但是这种做法导致最后的一个PWM信号输出到一半或其他时刻就被强制关闭输出了,最后一个信号不一定是一个完整的信号。

使用中断的方法也试过,每发一个PWM信号进入一次中断,当计数到100个脉冲后,也是强制关闭PWM输出

EPwm1Regs.TZFRC.bit.OST = 1; //强制TZ模式清除PWM---stop

EPwm2Regs.TZFRC.bit.OST = 1; //强制TZ模式清除PWM---stop

这个中断的方法结果和软件延时也差不多,就是当进入中断计数到最后一个脉冲时去软件强制关闭,PWM单元已经发出来一会了,所以最后一个波形也不是完整的,所以我想问下28069芯片的EPWM的控制寄存器里面是否可以配置输出PWM的个数,个数到了硬件自己关闭,或者是否还有其他处理的方法,输出若干个完整的PWM信号?