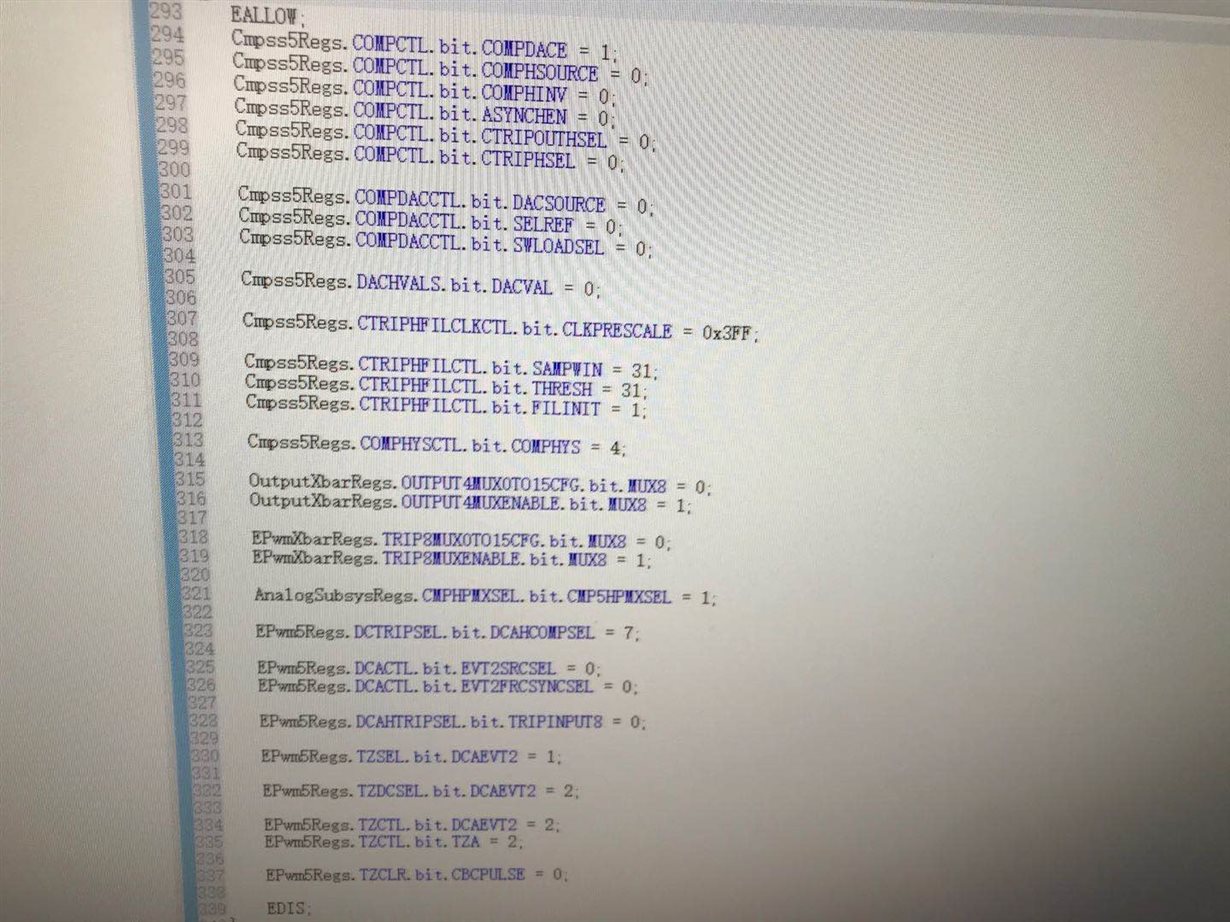

芯片型号F280049,通过内部比较器输出一个TRIP信号给PWM触发TZ关断周期为50%的PWM,现有几个问题请大家指点,如下:

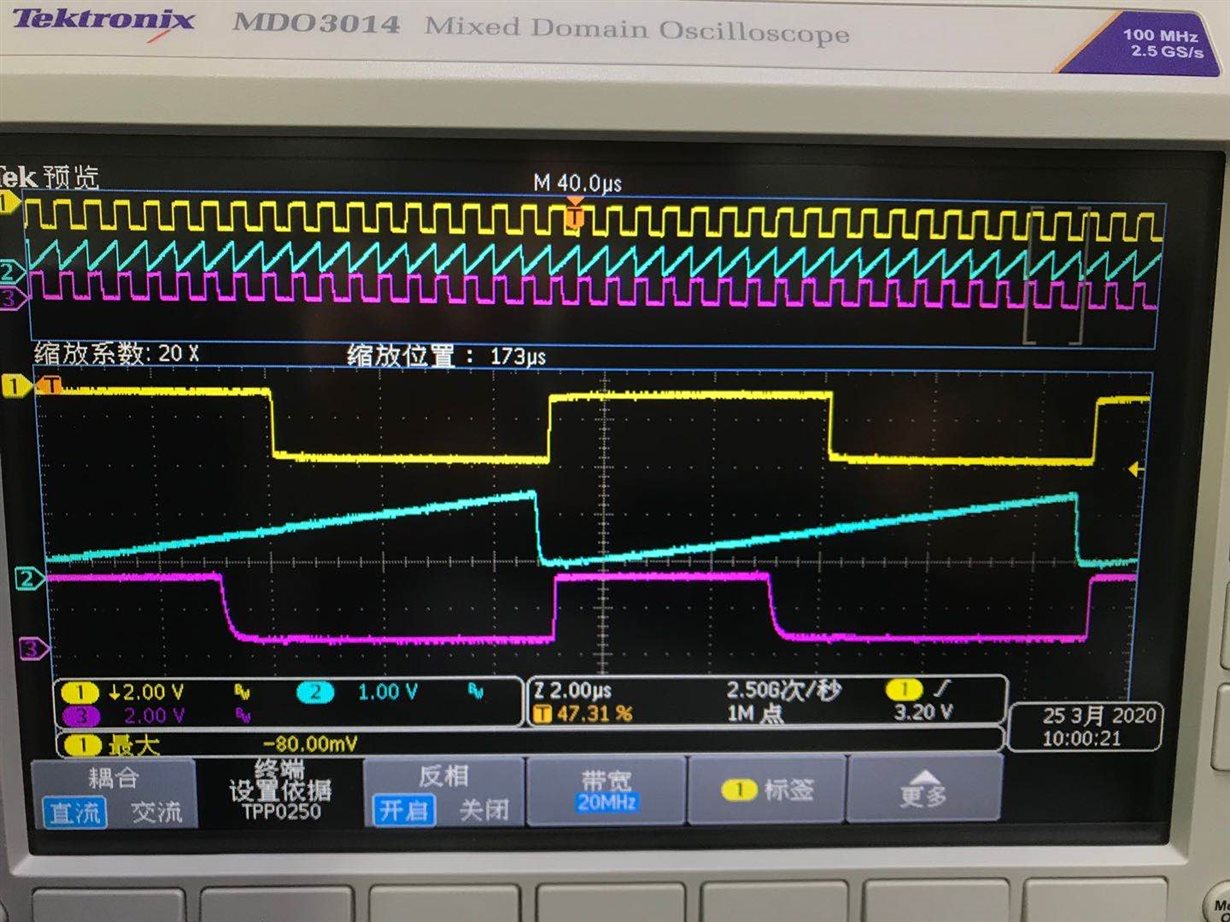

1:PWM程序配置为CBC方式,我的理解是在一个周期内只要触发一次后就会一直保持关断状态,实际结果是,当比较器的输出TRIP信号消失后,PWM立即恢复了输出。

2:CBC配置拉低的方式为置低,但是当TZ触发后PWM输出明显有一个软关状态,有点像配置为高阻状态了,这是什么原因导致的?

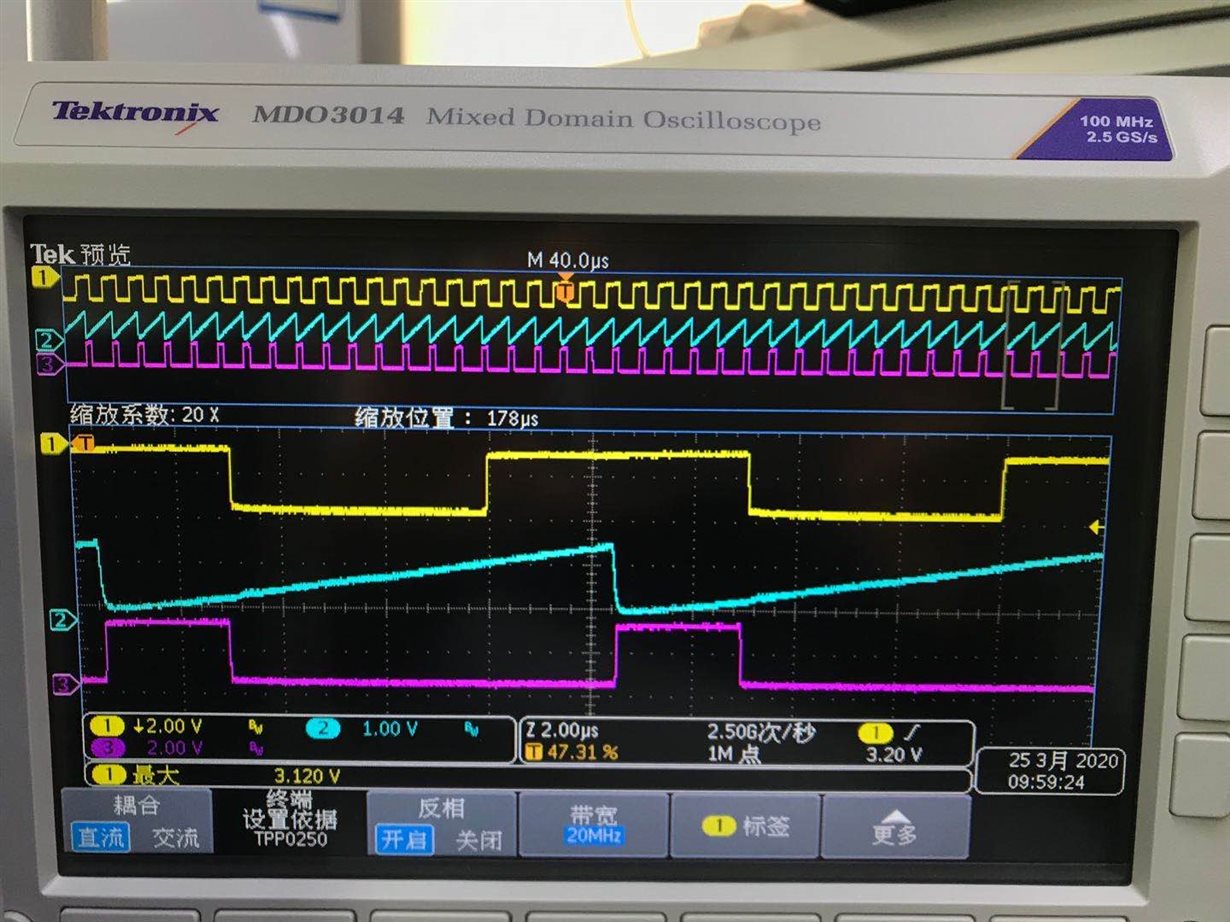

下图为测试波形:1通道为正常PWM的50%输出波形,2通道为送进内部比较器的模拟信号,比较值为0.7V,3通道为TZ状态后的PWM波形。