我的芯片是TMS320F28035,我测试了C2000Ware_3_02_00_00这个库里面的cla_adc这个例程,然后发现那个adc触发是pwm周期内多次触发,而不是pwm一次,adc触发cla一次。我把代码贴出来

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#include "CLAShared.h"

#include <string.h>

#include <stdint.h>

//

// Prototype statements

//

__interrupt void cla1_isr2(void);

//

// Globals

//

#pragma DATA_SECTION(ConversionCount, "Cla1ToCpuMsgRAM");

#pragma DATA_SECTION(VoltageCLA, "Cla1ToCpuMsgRAM");

Uint16 ConversionCount;

Uint16 LoopCount;

Uint16 VoltageCLA[NUM_DATA_POINTS];

extern Uint16 Cla1funcsLoadStart;

extern Uint16 Cla1funcsLoadSize;

extern Uint16 Cla1funcsRunStart;

void Gpio_select(void)

{

EALLOW;

GpioCtrlRegs.GPADIR.bit.GPIO12 = 0x01; // All outputs

GpioCtrlRegs.GPADIR.bit.GPIO24 = 0x01;

GpioCtrlRegs.GPBDIR.bit.GPIO34 = 0x01;

GpioDataRegs.GPADAT.bit.GPIO12 =0x01;

GpioDataRegs.GPADAT.bit.GPIO24 =0x01;

GpioDataRegs.GPBDAT.bit.GPIO34 =0x01;

EDIS;

}

void main(void)

{

Uint16 adc_tmp,adc_val;

InitSysCtrl();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW; // This is needed to write to EALLOW protected register

PieVectTable.CLA1_INT2 = &cla1_isr2;

EDIS; // This is needed to disable write to EALLOW protected registers

InitAdc(); // For this example, init the ADC

AdcOffsetSelfCal();

PieCtrlRegs.PIEIER11.bit.INTx2 = 1; // Enable INT 11.2 in PIE (CLA Task2)

IER |= M_INT11; // Enable CPU Interrupt 11

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

memcpy((uint16_t *)&Cla1funcsRunStart,(uint16_t *)&Cla1funcsLoadStart,

(unsigned long)&Cla1funcsLoadSize);

EALLOW;

Cla1Regs.MVECT2 = (Uint16)((Uint32)&Cla1Task2 - (Uint32)&Cla1Prog_Start);

Cla1Regs.MVECT8 = (Uint16)((Uint32)&Cla1Task8 - (Uint32)&Cla1Prog_Start);

Cla1Regs.MPISRCSEL1.bit.PERINT2SEL = CLA_INT2_ADCINT2;

Cla1Regs.MMEMCFG.bit.PROGE = 1; // Map CLA program memory to the CLA

Cla1Regs.MCTL.bit.IACKE = 1; // Enable IACK to start tasks via software

Cla1Regs.MIER.all = (M_INT8 | M_INT2); // Enable Task 8 and Task 2

Cla1ForceTask8andWait(); // Force CLA task 8.

// This will initialize ConversionCount to zero

AdcRegs.ADCCTL1.bit.INTPULSEPOS = 0;

AdcRegs.INTSEL1N2.bit.INT2E = 1; //Enable ADCINT2

AdcRegs.INTSEL1N2.bit.INT2CONT = 0; //Disable ADCINT2 Continuous mode

AdcRegs.INTSEL1N2.bit.INT2SEL = 1; //setup EOC1 to trigger ADCINT2 to fire

AdcRegs.ADCSOC1CTL.bit.CHSEL = 2; //set SOC1 channel select to ADCINA2

AdcRegs.ADCSOC1CTL.bit.TRIGSEL = 5; //set SOC1 start trigger on EPWM1A

AdcRegs.ADCSOC1CTL.bit.ACQPS = 6;

EDIS;

InitEPwm1Gpio();

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // PWM toggle high/low

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group

EPwm1Regs.ETSEL.bit.SOCASEL = 4; // Select SOC from from CPMA on upcount

EPwm1Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

EPwm1Regs.CMPA.half.CMPA = 0x2EE; // Set compare A value

EPwm1Regs.TBPRD = 0x5DC;

EPwm1Regs.TBCTL.bit.CTRMODE = 0; // count up and start

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

Gpio_select();

for(;;)

{

adc_val=ConversionCount;

adc_tmp=VoltageCLA[0];

LoopCount++;

}

}

__interrupt void cla1_isr2()

{

GpioDataRegs.GPATOGGLE.bit.GPIO24=1;

AdcRegs.ADCINTFLGCLR.bit.ADCINT2 = 1;

PieCtrlRegs.PIEACK.all = 0xFFFF;

}

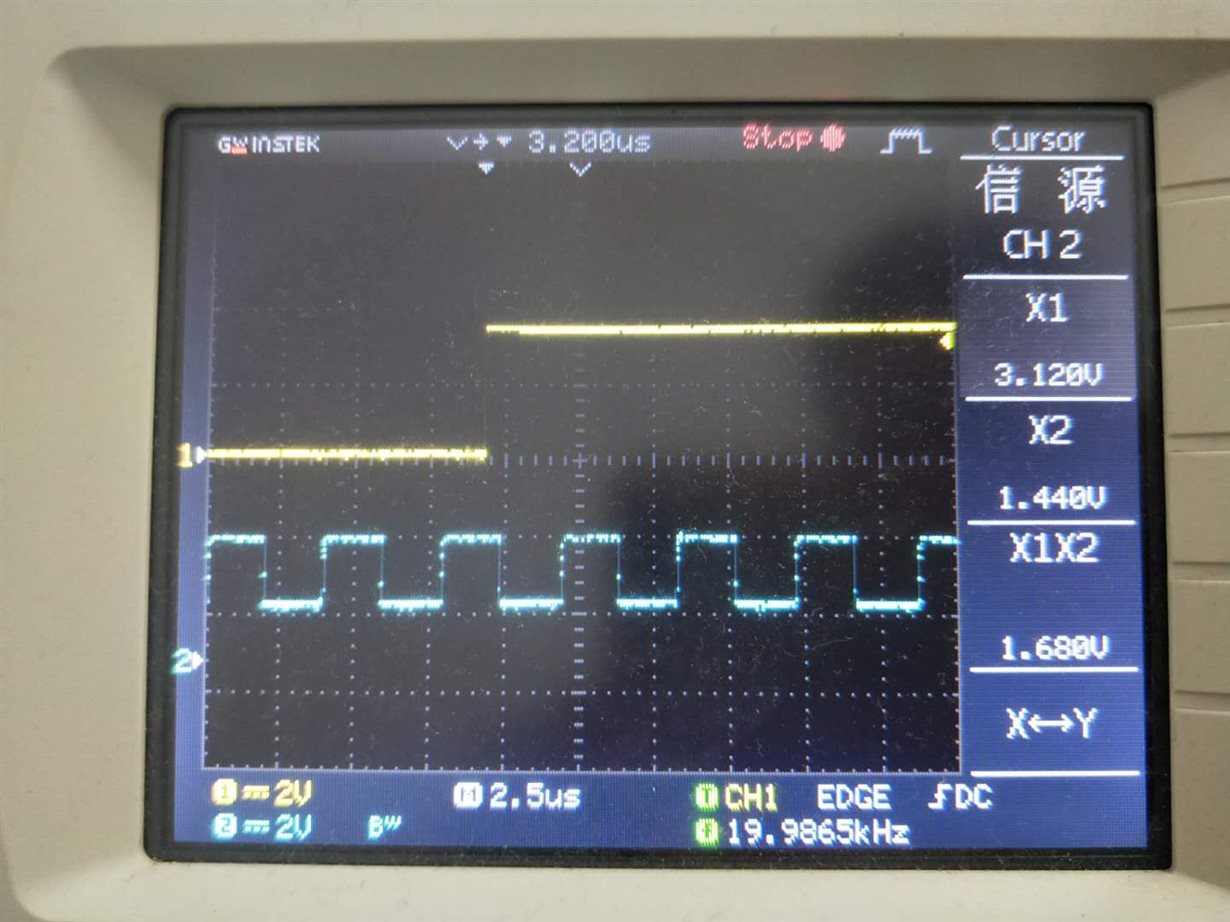

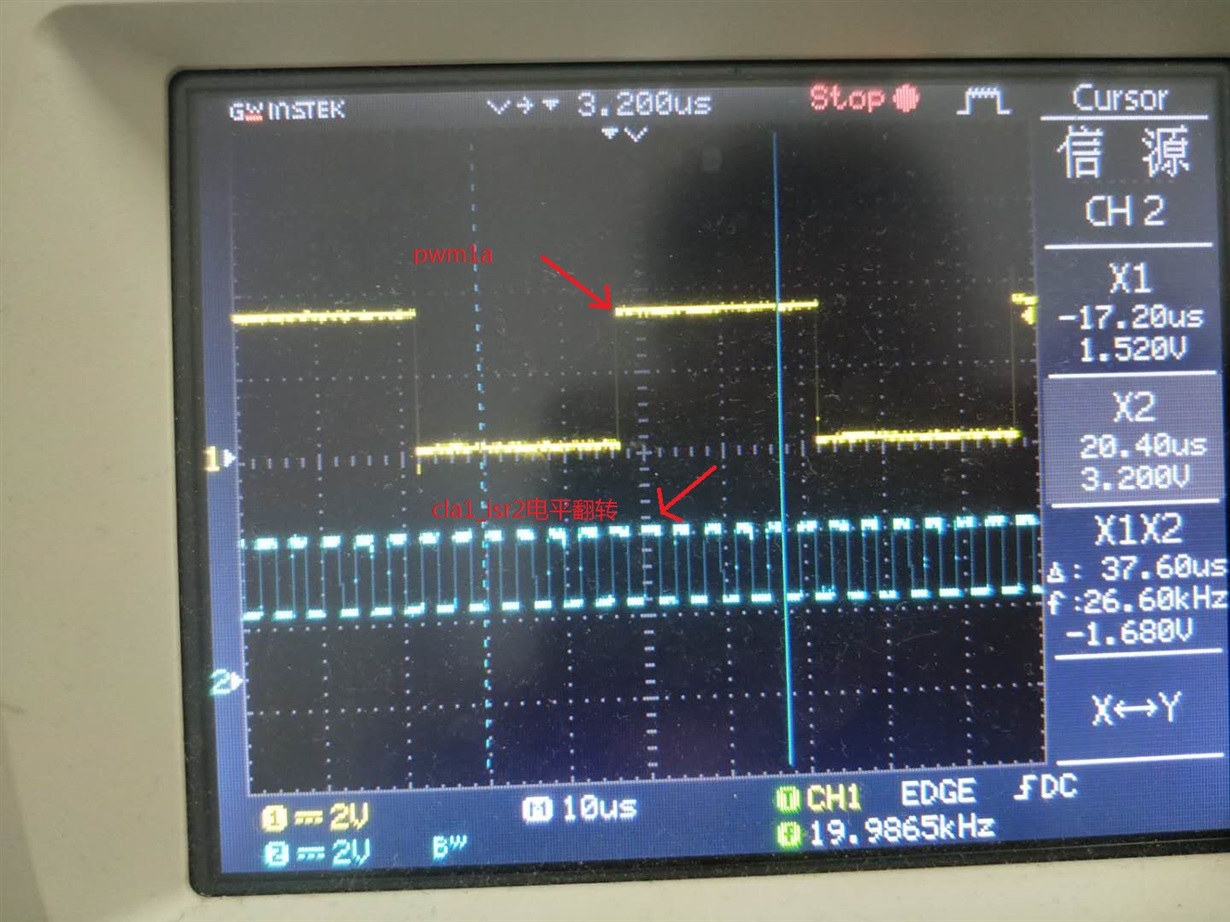

这个代码我就是把pwm1a的信号输出,还有就是在__interrupt void cla1_isr2()这个中断里面翻转了一下IO,然后抓取了pwm的波形跟__interrupt void cla1_isr2()中断的波形,发现pwm输出是20khz,而中断的频率到了250khz,跟我的理解不一样啊,我的理解应该是pwm一个周期应该产生一次adc触发,cla收到adc触发后,在Cla1Task2这个任务里转换一次adc,然后产生__interrupt void cla1_isr2()中断告知cpu,不知道我的理解是否正确。我把波形贴出来,大神帮我看看,为什么实际产生的波形跟我的理解有误差呢?

我的问题:

1、为什么那个__interrupt void cla1_isr2()中断不是pwm1a在一个周期内只产生1次?