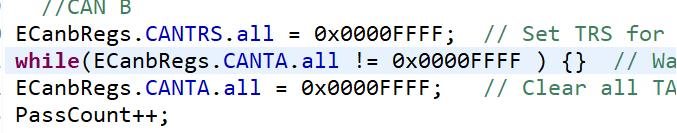

想同时利用DSP28335的CANA和CANB同时进行通信,在自响应测试(ACK)模式下,两路CAN均可以正常进行。但是,当设置为正常通讯模式时,CANB线路的信号总是会卡在ECanbRegs.CANTA.all != 0x0000FFFF的等待循环中,CAN总线上也监测不到任何响应。应该要如何修改呢?

CANB的配置完全是按照CANA的模式修改的,仅仅把ECana改成了ECanb,邮箱的地址进行了修改,保证没有冲突。是这里使用的不当吗?

具体代码如下:在ACK模式下,均可以正常运行,但是,在正常通讯模式下,ECANb会发送失败,在循环中卡住。

#include "DSP2833x_Device.h" // DSP2833x Headerfile Include File

#include "DSP2833x_Examples.h" // DSP2833x Examples Include File

// Global variable for this example

Uint32 MessageReceivedCount;

void main(void)

{

// eCAN control registers require read/write access using 32-bits. Thus we

// will create a set of shadow registers for this example. These shadow

// registers will be used to make sure the access is 32-bits and not 16.

struct ECAN_REGS ECanaShadow;

struct ECAN_REGS ECanbShadow;

// Step 1. Initialize System Control:

// PLL, WatchDog, enable Peripheral Clocks

// This example function is found in the DSP2833x_SysCtrl.c file.

InitSysCtrl();

// Step 2. Initalize GPIO:

// This example function is found in the DSP2833x_Gpio.c file and

// illustrates how to set the GPIO to it's default state.

// InitGpio(); // Skipped for this example

// For this example, configure CAN pins using GPIO regs here

// This function is found in DSP2833x_ECan.c

//InitECanGpio();

InitECanaGpio();

InitECanbGpio();

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the DSP2833x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in DSP2833x_DefaultIsr.c.

// This function is found in DSP2833x_PieVect.c.

InitPieVectTable();

// Step 4. Initialize all the Device Peripherals:

// This function is found in DSP2833x_InitPeripherals.c

// InitPeripherals(); // Not required for this example

// Step 5. User specific code, enable interrupts:

// eCAN control registers require 32-bit access.

// If you want to write to a single bit, the compiler may break this

// access into a 16-bit access. One solution, that is presented here,

// is to use a shadow register to force the 32-bit access.

// Read the entire register into a shadow register. This access

// will be 32-bits. Change the desired bit and copy the value back

// to the eCAN register with a 32-bit write.

// Configure the eCAN RX and TX pins for eCAN transmissions

EALLOW;

//CAN A

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

//CAN B

ECanbShadow.CANTIOC.all = ECanbRegs.CANTIOC.all;

ECanbShadow.CANTIOC.bit.TXFUNC = 1;

ECanbRegs.CANTIOC.all = ECanbShadow.CANTIOC.all;

ECanbShadow.CANRIOC.all = ECanbRegs.CANRIOC.all;

ECanbShadow.CANRIOC.bit.RXFUNC = 1;

ECanbRegs.CANRIOC.all = ECanbShadow.CANRIOC.all;

EDIS;

// Disable all Mailboxes

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANME.all = 0;

ECanbRegs.CANME.all = 0;

// Mailboxs can be written to 16-bits or 32-bits at a time

// Write to the MSGID field of TRANSMIT mailboxes MBOX0 - 15

//CAN A

ECanaMboxes.MBOX0.MSGID.all = 0x95550093;

ECanaMboxes.MBOX1.MSGID.all = 0x95550094;

ECanaMboxes.MBOX2.MSGID.all = 0x95550122;

ECanaMboxes.MBOX3.MSGID.all = 0x95550125;

ECanaMboxes.MBOX4.MSGID.all = 0x955501A1;

ECanaMboxes.MBOX5.MSGID.all = 0x955501A2;

ECanaMboxes.MBOX6.MSGID.all = 0x95550132;

ECanaMboxes.MBOX7.MSGID.all = 0x95550135;

ECanaMboxes.MBOX8.MSGID.all = 0x955501B1;

ECanaMboxes.MBOX9.MSGID.all = 0x955501B2;

ECanaMboxes.MBOX10.MSGID.all = 0x9555AAAA;

ECanaMboxes.MBOX11.MSGID.all = 0x9555AAAB;

ECanaMboxes.MBOX12.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX13.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX14.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX15.MSGID.all = 0x9555AAAF;

//CAN B

ECanbMboxes.MBOX0.MSGID.all = 0x9555B051;

ECanbMboxes.MBOX1.MSGID.all = 0x9555B052;

ECanbMboxes.MBOX2.MSGID.all = 0x9555B053;

ECanbMboxes.MBOX3.MSGID.all = 0x9555B054;

ECanbMboxes.MBOX4.MSGID.all = 0x9555B055;

ECanbMboxes.MBOX5.MSGID.all = 0x9555B056;

ECanbMboxes.MBOX6.MSGID.all = 0x9555B057;

ECanbMboxes.MBOX7.MSGID.all = 0x9555B058;

ECanbMboxes.MBOX8.MSGID.all = 0x9555B059;

ECanbMboxes.MBOX9.MSGID.all = 0x9555B060;

ECanbMboxes.MBOX10.MSGID.all = 0x9555B061;

ECanbMboxes.MBOX11.MSGID.all = 0x9555B062;

ECanbMboxes.MBOX12.MSGID.all = 0x9555B063;

ECanbMboxes.MBOX13.MSGID.all = 0x9555B064;

ECanbMboxes.MBOX14.MSGID.all = 0x9555B065;

ECanbMboxes.MBOX15.MSGID.all = 0x9555B066;

// Write to the MSGID field of RECEIVE mailboxes MBOX16 - 31

//CAN A

ECanaMboxes.MBOX16.MSGID.all = 0x95550093;

ECanaMboxes.MBOX17.MSGID.all = 0x95550094;

ECanaMboxes.MBOX18.MSGID.all = 0x95550122;

ECanaMboxes.MBOX19.MSGID.all = 0x95550125;

ECanaMboxes.MBOX20.MSGID.all = 0x955501A1;

ECanaMboxes.MBOX21.MSGID.all = 0x955501A2;

ECanaMboxes.MBOX22.MSGID.all = 0x95550132;

ECanaMboxes.MBOX23.MSGID.all = 0x95550135;

ECanaMboxes.MBOX24.MSGID.all = 0x955501B1;

ECanaMboxes.MBOX25.MSGID.all = 0x955501B2;

ECanaMboxes.MBOX26.MSGID.all = 0x95550093;

ECanaMboxes.MBOX27.MSGID.all = 0x95550094;

ECanaMboxes.MBOX28.MSGID.all = 0x9555AAAC;

ECanaMboxes.MBOX29.MSGID.all = 0x9555AAAD;

ECanaMboxes.MBOX30.MSGID.all = 0x9555AAAE;

ECanaMboxes.MBOX31.MSGID.all = 0x9555AAAF;

//CAN B

ECanbMboxes.MBOX16.MSGID.all = 0x9555B051;

ECanbMboxes.MBOX17.MSGID.all = 0x9555B052;

ECanbMboxes.MBOX18.MSGID.all = 0x9555B053;

ECanbMboxes.MBOX19.MSGID.all = 0x9555B054;

ECanbMboxes.MBOX20.MSGID.all = 0x9555B055;

ECanbMboxes.MBOX21.MSGID.all = 0x9555B056;

ECanbMboxes.MBOX22.MSGID.all = 0x9555B057;

ECanbMboxes.MBOX23.MSGID.all = 0x9555B058;

ECanbMboxes.MBOX24.MSGID.all = 0x9555B059;

ECanbMboxes.MBOX25.MSGID.all = 0x9555B060;

ECanbMboxes.MBOX26.MSGID.all = 0x9555B061;

ECanbMboxes.MBOX27.MSGID.all = 0x9555B062;

ECanbMboxes.MBOX28.MSGID.all = 0x9555B063;

ECanbMboxes.MBOX29.MSGID.all = 0x9555B064;

ECanbMboxes.MBOX30.MSGID.all = 0x9555B065;

ECanbMboxes.MBOX31.MSGID.all = 0x9555B066;

// Configure Mailboxes 0-15 as Tx, 16-31 as Rx

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANMD.all = 0xFFFF0000;

ECanbRegs.CANMD.all = 0xFFFF0000;

// Enable all Mailboxes */

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanbRegs.CANME.all = 0xFFFFFFFF;

ECanaRegs.CANME.all = 0xFFFFFFFF;

// Specify that 8 bits will be sent/received

//CAN A

ECanaMboxes.MBOX0.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX1.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX2.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX3.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX4.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX5.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX6.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX7.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX8.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX9.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX10.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX11.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX12.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX13.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX14.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX15.MSGCTRL.bit.DLC = 8;

//CAN B

ECanbMboxes.MBOX0.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX1.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX2.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX3.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX4.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX5.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX6.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX7.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX8.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX9.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX10.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX11.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX12.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX13.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX14.MSGCTRL.bit.DLC = 8;

ECanbMboxes.MBOX15.MSGCTRL.bit.DLC = 8;

// No remote frame is requested

// Since RTR bit is undefined upon reset,

// it must be initialized to the proper value

//CAN A

ECanaMboxes.MBOX0.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX1.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX2.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX3.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX4.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX5.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX6.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX7.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX8.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX9.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX10.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX11.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX12.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX13.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX14.MSGCTRL.bit.RTR = 0;

ECanaMboxes.MBOX15.MSGCTRL.bit.RTR = 0;

//CAN B

ECanbMboxes.MBOX0.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX1.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX2.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX3.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX4.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX5.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX6.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX7.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX8.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX9.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX10.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX11.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX12.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX13.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX14.MSGCTRL.bit.RTR = 0;

ECanbMboxes.MBOX15.MSGCTRL.bit.RTR = 0;

// Write to the mailbox RAM field of MBOX0 - 15

//CAN A

ECanaMboxes.MBOX0.MDL.all = 0xBF;

ECanaMboxes.MBOX0.MDH.all = 0x00;

ECanaMboxes.MBOX1.MDL.all = 0xB5;

ECanaMboxes.MBOX1.MDH.all = 0x00;

ECanaMboxes.MBOX2.MDL.all = 0xB4;

ECanaMboxes.MBOX2.MDH.all = 0x00;

ECanaMboxes.MBOX3.MDL.all = 0xBE;

ECanaMboxes.MBOX3.MDH.all = 0x00;

ECanaMboxes.MBOX4.MDL.all = 0x1;

ECanaMboxes.MBOX4.MDH.all = 0x00;

ECanaMboxes.MBOX5.MDL.all = 0x2;

ECanaMboxes.MBOX5.MDH.all = 0x00;

ECanaMboxes.MBOX6.MDL.all = 0xB4;

ECanaMboxes.MBOX6.MDH.all = 0x00;

ECanaMboxes.MBOX7.MDL.all = 0xBE;

ECanaMboxes.MBOX7.MDH.all = 0x00;

ECanaMboxes.MBOX8.MDL.all = 0x1;

ECanaMboxes.MBOX8.MDH.all = 0x00;

ECanaMboxes.MBOX9.MDL.all = 0x2;

ECanaMboxes.MBOX9.MDH.all = 0x00;

ECanaMboxes.MBOX10.MDL.all = 0x9555AAAA;

ECanaMboxes.MBOX10.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX11.MDL.all = 0x9555AAAB;

ECanaMboxes.MBOX11.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX12.MDL.all = 0x9555AAAC;

ECanaMboxes.MBOX12.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX13.MDL.all = 0x9555AAAD;

ECanaMboxes.MBOX13.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX14.MDL.all = 0x9555AAAE;

ECanaMboxes.MBOX14.MDH.all = 0x89ABCDEF;

ECanaMboxes.MBOX15.MDL.all = 0x9555AAAF;

ECanaMboxes.MBOX15.MDH.all = 0x89ABCDEF;

//CAN B

ECanbMboxes.MBOX0.MDL.all = 0xBFB;

ECanbMboxes.MBOX0.MDH.all = 0x00B;

ECanbMboxes.MBOX1.MDL.all = 0xB5B;

ECanbMboxes.MBOX1.MDH.all = 0x00B;

ECanbMboxes.MBOX2.MDL.all = 0xB4B;

ECanbMboxes.MBOX2.MDH.all = 0x00B;

ECanbMboxes.MBOX3.MDL.all = 0xBEB;

ECanbMboxes.MBOX3.MDH.all = 0x00B;

ECanbMboxes.MBOX4.MDL.all = 0x1B;

ECanbMboxes.MBOX4.MDH.all = 0x00B;

ECanbMboxes.MBOX5.MDL.all = 0x2B;

ECanbMboxes.MBOX5.MDH.all = 0x00B;

ECanbMboxes.MBOX6.MDL.all = 0xB4B;

ECanbMboxes.MBOX6.MDH.all = 0x00B;

ECanbMboxes.MBOX7.MDL.all = 0xBEB;

ECanbMboxes.MBOX7.MDH.all = 0x00B;

ECanbMboxes.MBOX8.MDL.all = 0x1B;

ECanbMboxes.MBOX8.MDH.all = 0x00B;

ECanbMboxes.MBOX9.MDL.all = 0x2B;

ECanbMboxes.MBOX9.MDH.all = 0x00B;

ECanbMboxes.MBOX10.MDL.all = 0x9555BAAA;

ECanbMboxes.MBOX10.MDH.all = 0x89ABCDEB;

ECanbMboxes.MBOX11.MDL.all = 0x9555BAAB;

ECanbMboxes.MBOX11.MDH.all = 0x89ABCDEB;

ECanbMboxes.MBOX12.MDL.all = 0x9555BAAC;

ECanbMboxes.MBOX12.MDH.all = 0x89ABCDEB;

ECanbMboxes.MBOX13.MDL.all = 0x9555BAAD;

ECanbMboxes.MBOX13.MDH.all = 0x89ABCDEB;

ECanbMboxes.MBOX14.MDL.all = 0x9555BAAE;

ECanbMboxes.MBOX14.MDH.all = 0x89ABCDEB;

ECanbMboxes.MBOX15.MDL.all = 0x9555BAAF;

ECanbMboxes.MBOX15.MDH.all = 0x89ABCDEB;

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

EALLOW;

ECanaRegs.CANMIM.all = 0xFFFFFFFF;

ECanbRegs.CANMIM.all = 0xFFFFFFFF;

// Request permission to change the configuration registers

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 1;

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

EDIS;

// Wait until the CPU has been granted permission to change the

// configuration registers

// Wait for CCE bit to be set..

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 );

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 1 );

// Configure the eCAN timing

EALLOW;

//CAN A

ECanaShadow.CANBTC.all = ECanaRegs.CANBTC.all;

ECanaShadow.CANBTC.bit.BRPREG = 9; // (BRPREG + 1) = 10 feeds a 15 MHz CAN clock

ECanaShadow.CANBTC.bit.TSEG2REG = 5 ; // to the CAN module. (150 / 10 = 15)

ECanaShadow.CANBTC.bit.TSEG1REG = 7; // Bit time = 15

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

//CAN B

ECanbShadow.CANBTC.all = ECanbRegs.CANBTC.all;

ECanbShadow.CANBTC.bit.BRPREG = 9; // (BRPREG + 1) = 10 feeds a 15 MHz CAN clock

ECanbShadow.CANBTC.bit.TSEG2REG = 5 ; // to the CAN module. (150 / 10 = 15)

ECanbShadow.CANBTC.bit.TSEG1REG = 7; // Bit time = 15

ECanbRegs.CANBTC.all = ECanbShadow.CANBTC.all;

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.CCR = 0;

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

EDIS;

// Wait until the CPU no longer has permission to change the

// configuration registers

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 );

do

{

ECanbShadow.CANES.all = ECanbRegs.CANES.all;

} while(ECanbShadow.CANES.bit.CCE != 0 );

// Configure the eCAN for normal mode

// Enable the enhanced features of the eCAN.

EALLOW;

//CAN A

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.STM = 0; // Configure CAN for normal mode

ECanaShadow.CANMC.bit.SCB = 1; // eCAN mode (reqd to access 32 mailboxes)

ECanaShadow.CANMC.bit.ABO = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

//CAN B

ECanbShadow.CANMC.all = ECanbRegs.CANMC.all;

ECanbShadow.CANMC.bit.STM = 0; // Configure CAN for normal mode

ECanbShadow.CANMC.bit.SCB = 1; // eCAN mode (reqd to access 32 mailboxes)

ECanbShadow.CANMC.bit.ABO = 1;

ECanbRegs.CANMC.all = ECanbShadow.CANMC.all;

EDIS;

// Begin transmitting

MessageReceivedCount=0;

for(;;)

{

//CAN A

ECanaRegs.CANTRS.all = 0x0000FFFF; // Set TRS for all transmit mailboxes

while(ECanaRegs.CANTA.all != 0x0000FFFF ) {} // Wait for all TAn bits to be set..

ECanaRegs.CANTA.all = 0x0000FFFF; // Clear all TAn

MessageReceivedCount++;

//CAN B

ECanbRegs.CANTRS.all = 0x0000FFFF; // Set TRS for all transmit mailboxes

while(ECanbRegs.CANTA.all != 0x0000FFFF ) {} // Wait for all TAn bits to be set..

ECanbRegs.CANTA.all = 0x0000FFFF; // Clear all TAn

}

}