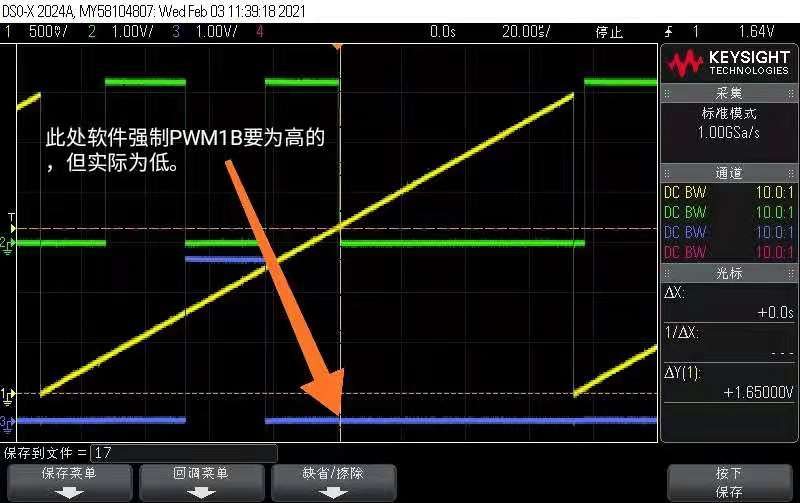

程序说明:使用模拟比较器产生数字比较器事件,强制使PWM1A为低,强制使PWM1B为高。但实测PWM1B波形应该为高电平却为低电平,折腾了好几天,都没解决。请TI工程师和大家帮我看下,是不是配置有不对。

void Init_Comp(void)

{

EALLOW;

GpioCtrlRegs.AIOMUX1.bit.AIO2 = 2; // CMP1A,即模拟比较器+输入

Comp1Regs.COMPCTL.bit.COMPDACEN = 1; //DAC逻辑上电

Comp1Regs.COMPCTL.bit.COMPSOURCE = 0; // 比较器负极接DAC,即模拟比较器-输入

Comp1Regs.COMPCTL.bit.CMPINV = 0; // 同相输出,过流输出高

Comp1Regs.COMPCTL.bit.QUALSEL = 0x09;

Comp1Regs.COMPCTL.bit.SYNCSEL = 1; // 比较器输出在经过ETPWM/GPIO模块前进行同步

Comp1Regs.DACCTL.bit.DACSOURCE = 0; // DACVAL控制DAC

Comp1Regs.DACVAL.all = 0x0200; // 1.65V

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT; // DCAH输入的源是COMP1OUT

EPwm1Regs.TZDCSEL.bit.DCAEVT2 = TZ_DCAH_HI; // DCAH为高时DCAEVT2有效(输出高)

EPwm1Regs.DCACTL.bit.EVT2SRCSEL = DC_EVT2; // DCAEVT2信号不经过滤波,直通。

EPwm1Regs.DCACTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC; // 异步,无需同步。

EPwm1Regs.TZSEL.bit.DCAEVT2 = 1; // 允许DCAEVT2作为ePWM1A的周期触发源。

EPwm1Regs.TZCTL.bit.DCAEVT2 = TZ_FORCE_LO; // 强制EPWM1A处于低电平

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_COMP1OUT; // DCBH输入的源是COMP1OUT,过流时COMP1OUT为高,

EPwm1Regs.TZDCSEL.bit.DCBEVT2 = TZ_DCBH_HI; // DCBH为高时DCAEVT2有效(输出高)

EPwm1Regs.DCBCTL.bit.EVT2SRCSEL = DC_EVT2; // DCBEVT2信号不经过滤波,直通。

EPwm1Regs.DCBCTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC; // 异步,无需同步。

EPwm1Regs.TZSEL.bit.DCBEVT2 = 1; // 允许DCBEVT2作为ePWM1B的周期触发源。

EPwm1Regs.TZCTL.bit.DCBEVT2 = TZ_FORCE_HI; // 强制EPWM1B处于高电平

EDIS;

}

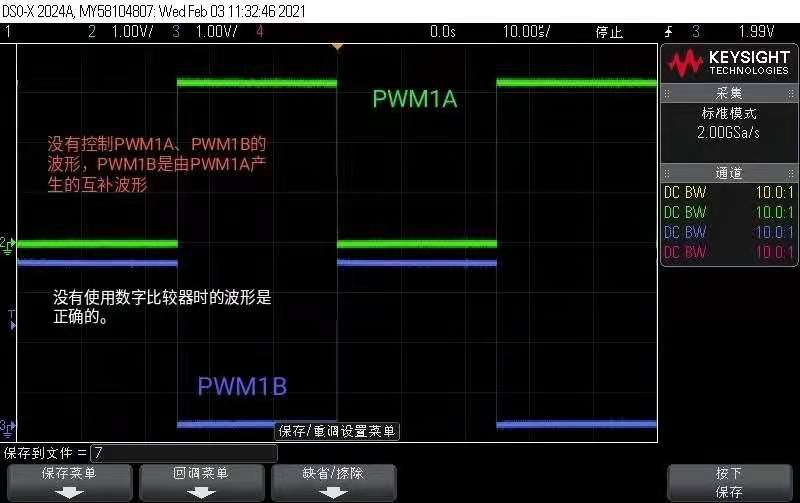

下图是没有使用数字比较器时的波形如下,PWM1A和PWM1B互补,是对的。

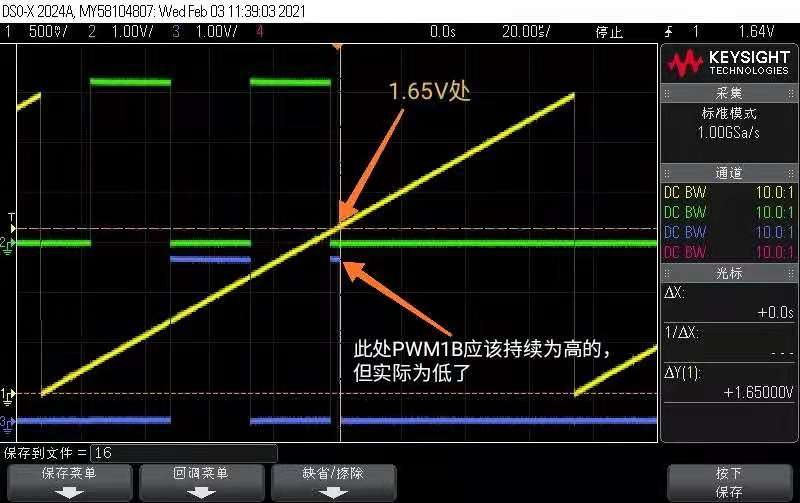

如程序那样,使用了模拟比较器产生数字比较器事件后,波形始下: