您好:

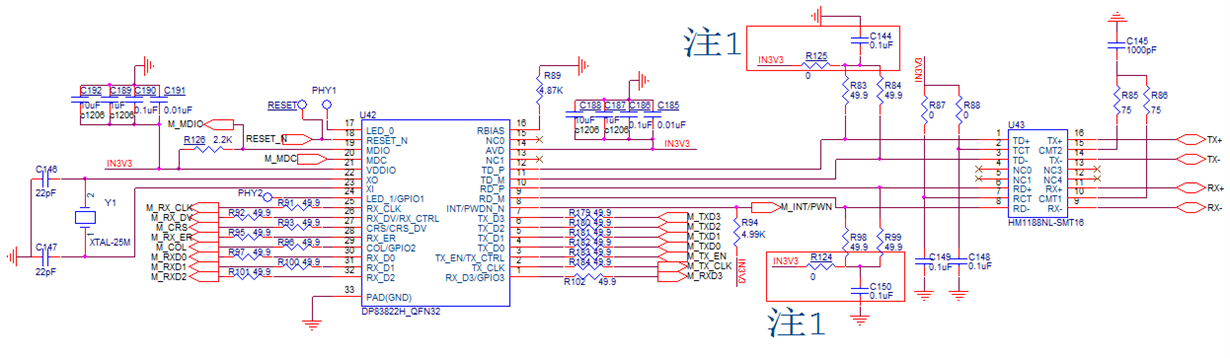

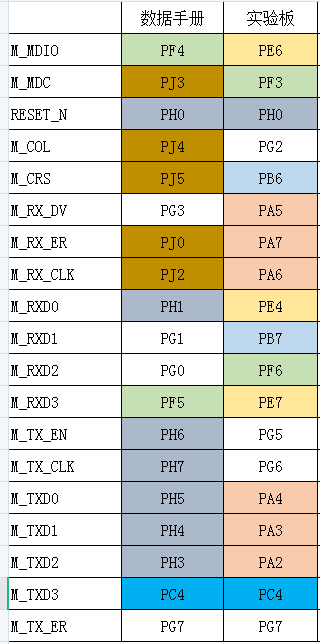

我采用F28M35X设备,采用了以太网外设功能,采用F28M35+DP83822设备,采用MII协议。分配了DSP相应引脚后,烧写了F28M35X的以太网例程(enet_uip),更改了例程中以太网引脚的分配,在电脑主机设置同一网段和掩码,ping开发板设备,提示“无法访问目标主机”,ping不通。

请各位专家帮忙审核,我的F28M35的以太网外设引脚分配是否有误?是否还有类似PB7的特殊引脚需要处理?

1、DSP及DP83822测量供电电压、时钟、复位引脚正常。DP83822的PHY地址选择默认0X01。

2、RXCLK为25MHz,TXCLK为25MHz,mdc时钟为2.2MHz,读PHYX芯片(DP83822)工作状态正常,link建立,全双工,100M,自协商。

3、选择F28M35的官方例程,enet_uip工程。

void EthernetPinsSetup(void)

{

//Ethernet pin setup

GPIODirModeSet(

GPIO_PORTA_BASE, GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4|

GPIO_PIN_3|GPIO_PIN_2, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(

GPIO_PORTA_BASE, GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4|

GPIO_PIN_3|GPIO_PIN_2, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PA7_MIIRXER);

GPIOPinConfigure(GPIO_PA6_MIIRXCK);

GPIOPinConfigure(GPIO_PA5_MIIRXDV);

GPIOPinConfigure(GPIO_PA4_MIITXD0);

GPIOPinConfigure(GPIO_PA3_MIITXD1);

GPIOPinConfigure(GPIO_PA2_MIITXD2);

GPIODirModeSet(GPIO_PORTB_BASE, GPIO_PIN_6, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_6, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PB6_MIICRS);

GPIODirModeSet(GPIO_PORTC_BASE, GPIO_PIN_4, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTC_BASE, GPIO_PIN_4, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PC4_MIITXD3);

GPIODirModeSet(GPIO_PORTE_BASE, GPIO_PIN_4|GPIO_PIN_6|GPIO_PIN_7, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTE_BASE, GPIO_PIN_4|GPIO_PIN_6|GPIO_PIN_7, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PE6_MIIMDIO);

GPIOPinConfigure(GPIO_PE7_MIIRXD3);

GPIOPinConfigure(GPIO_PE4_MIIRXD0);

GPIODirModeSet(GPIO_PORTF_BASE, GPIO_PIN_6|GPIO_PIN_3, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTF_BASE, GPIO_PIN_6|GPIO_PIN_3, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PF6_MIIRXD2);

GPIOPinConfigure(GPIO_PF3_MIIMDC);

GPIODirModeSet(GPIO_PORTG_BASE, GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_2,

GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTG_BASE, GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_2,

GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PG2_MIICOL);

GPIOPinConfigure(GPIO_PG5_MIITXEN);

GPIOPinConfigure(GPIO_PG6_MIITXCLK);

GPIOPinConfigure(GPIO_PG7_MIITXER);

GPIODirModeSet(GPIO_PORTH_BASE, GPIO_PIN_0, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTH_BASE, GPIO_PIN_0, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PH0_MIIPHYRSTn);

GPIODirModeSet(GPIO_PORTJ_BASE, GPIO_PIN_6, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTJ_BASE, GPIO_PIN_6, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PJ6_MIIPHYINTRn);

// Convert the PB7/NMI pin into a GPIO pin. This requires the use of the

// GPIO lock since changing the state of the pin is otherwise disabled.

//

HWREG(GPIO_PORTB_BASE + GPIO_O_LOCK) = GPIO_LOCK_KEY_DD;

HWREG(GPIO_PORTB_BASE + GPIO_O_CR) = 0x80;

//

GPIODirModeSet(GPIO_PORTB_BASE, GPIO_PIN_7, GPIO_DIR_MODE_HW);

GPIOPadConfigSet(GPIO_PORTB_BASE, GPIO_PIN_7, GPIO_PIN_TYPE_STD);

GPIOPinConfigure(GPIO_PB7_MIIRXD1);

// Clear the commit register, effectively locking access to registers

// controlling the PB7 configuration.

//

HWREG(GPIO_PORTB_BASE + GPIO_O_LOCK) = GPIO_LOCK_KEY_DD;

HWREG(GPIO_PORTB_BASE + GPIO_O_CR) = 0x00;

}