您好,请问一下,28035 cla0 这句限制是什么意思?是CPU和CLA公共RAM区,cla写入或是读取访问时,CPU不能进行读取和写入吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您可以看一下数据手册的 Figure 6-1. 28034/28035 Memory Map

https://www.ti.com.cn/cn/lit/ds/symlink/tms320f28035.pdf

会有

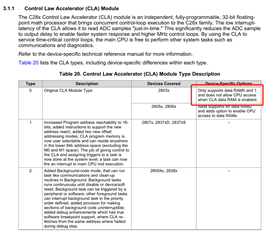

以及6.9.1 Control Law Accelerator (CLA) Overview

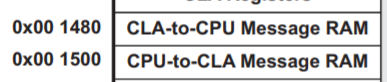

Memory and Shared Peripherals:

– Two dedicated message RAMs for communication between the CLA and the main CPU.

– The C28x CPU can map CLA program and data memory to the main CPU space or CLA space.

您好,感谢您的回复,从您给我的回复以及资料中,说明两者确实能进行数据交互,而且我还想请问一下:

1.问题中红框的意思,28035中不允许CPU访问CLA的RAM,也就是RAM0和RAM1,那28377中是允许CPU访问CLA的RAM,不用将变量设置到CLA-to-CPU RAM区和CPU-to-CLA区了吗?

2.两者是否能够同时访问CLA-to-CPU RAM区和CPU-to-CLA区,如果不能同时访问,这个时间是根据什么定的呢?

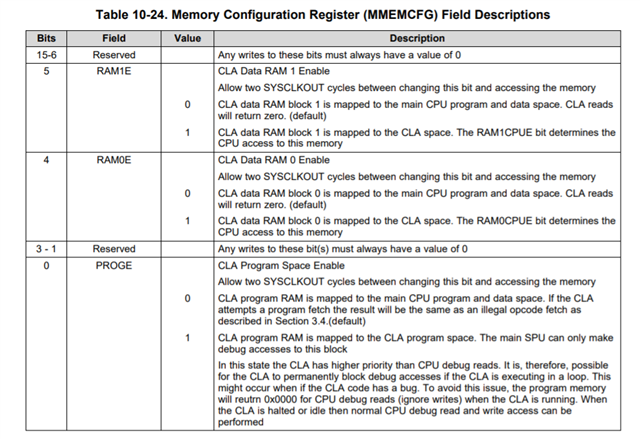

3.另外,以下三句话的具体含义是什么?

Cla1Regs.MMEMCFG.bit.PROGE = 1;

Cla1Regs.MMEMCFG.bit.RAM0E = CLARAM0_ENABLE;

Cla1Regs.MMEMCFG.bit.RAM1E = CLARAM1_ENABLE;

问题中红框的意思,28035中不允许CPU访问CLA的RAM,也就是RAM0和RAM1,那28377中是允许CPU访问CLA的RAM,不用将变量设置到CLA-to-CPU RAM区和CPU-to-CLA区了吗?

是的,您的理解是正确的。两者CLA类型是不同的

2.两者是否能够同时访问CLA-to-CPU RAM区和CPU-to-CLA区,如果不能同时访问,这个时间是根据什么定的呢?

理论上是可以的,cla和cpu是相对独立的

另外,以下三句话的具体含义是什么?

您可以看一下用户指南的 https://www.ti.com.cn/cn/lit/ug/sprui10/sprui10.pdf

10.7.3.2 Memory Configuration Register (MMEMCFG)

您好,感谢您的回复,我想再确认一下28377中是否需要公共区进行数据交互?

我想再确认一下28377中是否需要公共区进行数据交互?

是的

既然28377等也需要公共区进行数据交互,不能直接访问,那红框表明的具体是什么意思呢?

红框表示当CLA RAM使能的时候,cpu不能访问

网络有一些比较好的分享文章,您也可以看一下