你好:

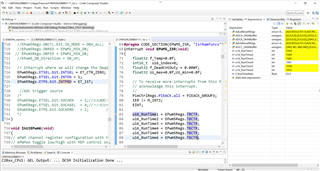

在程序中,通过EPWM5,在ET_CTR_ZERO时刻使能中断,配置如下:

// Interrupt where we will change the Deadband

EPwm5Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Prd event

EPwm5Regs.ETSEL.bit.INTEN = 1; // Enable INT

EPwm5Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

但是在程序中,通过读取初始段TBCRT数值,发现始终是从TBPRD开始的下降过程,感觉这个与配置不符

尝试将触发时刻更改为PRD时刻,读取的数值还是从从TBPRD开始的下降过程,

感觉始终是从PRD进入,这个配置对中断进入时刻没有影响,与配置文件不符,反复核查配置文件,没有发现为什么一直是PRD时刻进入中断,能不能帮忙看一下什么原因,多谢。

附件为PWM配置文件。

#include "f28004x_device.h" // Header File Include File

#include <Drv_config.h> // Examples Include File

//---------------------------------------------------------------------------

// InitEPwm:

//---------------------------------------------------------------------------

// This function initializes the ePWM(s) to a known state.

//

void InitEPwm(void)

{

// Initialize ePWM

InitEPwm1Gpio();

InitEPwm2Gpio();

InitEPwm3Gpio();

InitEPwm4Gpio();

InitEPwm5Gpio();

InitEPwm6Gpio();

InitEPwmFAN();

InitTz();//

//mOffDcdcPwm();

InitEPwm1();

InitEPwm2();

InitEPwm3();

InitEPwm4();

InitEPwm5();

InitEPwm6();

InitEPwm7(); //Trigger ADCSOC

InitEPwm8(); //FAN PWM

EALLOW;

EPwm1Regs.TBCTL.bit.SWFSYNC = 1; //���ͬ��һ��DC�ĸ�PWM���ع�,1Ϊmaster

EDIS;

}

void InitEPwm1Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO0 = 0; // Enable pullup on GPIO0

//GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0; // Enable pullup on GPIO1

GpioCtrlRegs.GPAPUD.bit.GPIO0 = 1; // Disable pull-up on GPIO0 (EPWM1A)

GpioCtrlRegs.GPAPUD.bit.GPIO1 = 1; // Disable pull-up on GPIO1 (EPWM1B)

/* Configure EPWM-1 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM1 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1; // Configure GPIO0 as EPWM1A

GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1; // Configure GPIO1 as EPWM1B

EDIS;

}

void InitEPwm2Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins

for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO2 = 0; // Enable pullup on GPIO2

//GpioCtrlRegs.GPAPUD.bit.GPIO3 = 0; // Enable pullup on GPIO3

GpioCtrlRegs.GPAPUD.bit.GPIO2 = 1; // Disable pull-up on GPIO2 (EPWM2A)

GpioCtrlRegs.GPAPUD.bit.GPIO3 = 1; // Disable pull-up on GPIO3 (EPWM2B)

/* Configure EPwm-2 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM2 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO2 = 1; // Configure GPIO2 as EPWM2A

GpioCtrlRegs.GPAMUX1.bit.GPIO3 = 1; // Configure GPIO3 as EPWM2B

EDIS;

}

void InitEPwm3Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins

for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO4 = 0; // Enable pullup on GPIO4

//GpioCtrlRegs.GPAPUD.bit.GPIO5 = 0; // Enable pullup on GPIO5

GpioCtrlRegs.GPAPUD.bit.GPIO4 = 1; // Disable pull-up on GPIO4 (EPWM3A)

GpioCtrlRegs.GPAPUD.bit.GPIO5 = 1; // Disable pull-up on GPIO5 (EPWM3B)

/* Configure EPwm-3 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM3 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO4 = 1; // Configure GPIO4 as EPWM3A

GpioCtrlRegs.GPAMUX1.bit.GPIO5 = 1; // Configure GPIO5 as EPWM3B

EDIS;

}

void InitEPwm4Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins

for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO6 = 1; // Enable pull-up on GPIO6 (EPWM4A)

//GpioCtrlRegs.GPAPUD.bit.GPIO7 = 1; // Enable pull-up on GPIO7 (EPWM4B)

GpioCtrlRegs.GPAPUD.bit.GPIO6 = 1; // Disable pull-up on GPIO6 (EPWM4A)

GpioCtrlRegs.GPAPUD.bit.GPIO7 = 1; // Disable pull-up on GPIO7 (EPWM4B)

/* Configure EPWM-4 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM4 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 1; // Configure GPIO6 as EPWM4A

GpioCtrlRegs.GPAMUX1.bit.GPIO7 = 1; // Configure GPIO7 as EPWM4B

EDIS;

}

void InitEPwm5Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO8 = 1; // Enable pull-up on GPIO8 (EPWM5A)

//GpioCtrlRegs.GPAPUD.bit.GPIO9 = 1; // Enable pull-up on GPIO9 (EPWM5B)

GpioCtrlRegs.GPAPUD.bit.GPIO8 = 1; // Disable pull-up on GPIO8 (EPWM5A)

GpioCtrlRegs.GPAPUD.bit.GPIO9 = 1; // Disable pull-up on GPIO9 (EPWM5B)

/* Configure EPWM-5 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM5 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO8 = 1; // Configure GPIO8 as EPWM5A,not GPIO

GpioCtrlRegs.GPAMUX1.bit.GPIO9 = 1; // Configure GPIO9 as EPWM5B,not GPIO

EDIS;

}

void InitEPwm6Gpio(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO10 = 0; // Disable pull-up on GPIO10 (EPWM6A)

//GpioCtrlRegs.GPAPUD.bit.GPIO11 = 0; // Disable pull-up on GPIO11 (EPWM6B)

GpioCtrlRegs.GPAPUD.bit.GPIO10 = 1; // Disable pull-up on GPIO10 (EPWM6A)

GpioCtrlRegs.GPAPUD.bit.GPIO11 = 1; // Disable pull-up on GPIO11 (EPWM6B)

/* Configure EPWM-6 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM6 functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 1; // Configure GPIO10 as GPIO,not EPWM6A

GpioCtrlRegs.GPAMUX1.bit.GPIO11 = 1; // Configure GPIO11 as GPIO,not EPWM6B

EDIS;

}

void InitEPwmFAN(void)

{

EALLOW;

/* Disable or Enable internal pull-up for the selected output pins for reduced power consumption */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAPUD.bit.GPIO10 = 0; // Disable pull-up on GPIO10 (EPWM6A)

//GpioCtrlRegs.GPAPUD.bit.GPIO11 = 0; // Disable pull-up on GPIO11 (EPWM6B)

//GpioCtrlRegs.GPAPUD.bit.GPIO10 = 1; // Disable pull-up on GPIO10 (EPWM6A)

GpioCtrlRegs.GPAPUD.bit.GPIO15 = 1; // Disable pull-up on GPIO11 (EPWM6B)

/* Configure EPWM-6 pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be EPWM6 functional pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAMUX1.bit.GPIO10 = 1; // Configure GPIO10 as GPIO,not EPWM6A

GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 1; // Configure GPIO11 as GPIO,not EPWM6B

EDIS;

}

void InitTz()

{

//EPwm1

EALLOW;

EPwm1Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm1Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm1Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm1Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm1Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

//EPwm2

EALLOW;

EPwm2Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm2Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm2Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm2Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm2Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm2Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm2Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

//EPwm3

EALLOW;

EPwm3Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm3Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm3Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm3Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm3Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm3Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm3Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm3Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

//EPwm4

EALLOW;

EPwm4Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm4Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm4Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm4Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm4Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm4Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm4Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm4Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

//EPwm5

EALLOW;

EPwm5Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm5Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm5Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm5Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm5Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm5Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm5Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm5Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm5Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

//EPwm6

EALLOW;

EPwm6Regs.TZCLR.bit.CBC = 1; //Clear trip

EPwm6Regs.TZSEL.bit.CBC1 = 1; //CBC

EPwm6Regs.TZCTL.bit.TZA = TZ_FORCE_LO;///TZ_FORCE_LO;

EPwm6Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm6Regs.TZDCSEL.bit.DCBEVT2 =0x2;//DCBH = high, DCBL = don't care

// 001: DCBH = low, DCBL = don't care

// 010: DCBH = high, DCBL = don't care

// 011: DCBL = low, DCBH = don't care

// 100: DCBL = high, DCBH = don't care

// 101: DCBL = high, DCBH = low

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT4 = 1;//ѡ����բ����4��ΪDCBH mux����ϡ�������

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT5 = 1;

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT8 = 1;

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT9 = 1;

EPwm6Regs.DCBHTRIPSEL.bit.TRIPINPUT10 = 1;

EPwm6Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xf;//TZ����������Ȩ����

EPwm6Regs.TZSEL.bit.DCBEVT2 =0x01;//�Ƚ������B CBC trip source

EPwm6Regs.DCBCTL.bit.EVT2SRCSEL = 0;

EDIS;

InitTzXbar();

}

void InitTzXbar(void)

{

EALLOW;

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX2 =0x0;// 00 : Select .0 input for Mux0

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX2 =0x1;//Mux0����Ӧ���������������;

EPwmXbarRegs.TRIP5MUX0TO15CFG.bit.MUX3 =0x0;// 00 : Select .0 input for Mux0

EPwmXbarRegs.TRIP5MUXENABLE.bit.MUX3 =0x1;//Mux0����Ӧ���������������;

EPwmXbarRegs.TRIP7MUX0TO15CFG.bit.MUX6 = 0x0;

EPwmXbarRegs.TRIP7MUXENABLE.bit.MUX6 = 0x1;

EPwmXbarRegs.TRIP8MUX0TO15CFG.bit.MUX7 = 0x0;

EPwmXbarRegs.TRIP8MUXENABLE.bit.MUX7 = 0x1;

EPwmXbarRegs.TRIP9MUX0TO15CFG.bit.MUX8 = 0x0;

EPwmXbarRegs.TRIP9MUXENABLE.bit.MUX8 = 0x1;

EPwmXbarRegs.TRIP10MUX0TO15CFG.bit.MUX9 = 0x0;

EPwmXbarRegs.TRIP10MUXENABLE.bit.MUX9 = 0x1;

EDIS;

}

void InitEPwm1(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM2 config config for PWM2A/2B

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm1Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm1Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm1Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm1Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm1Regs.CMPB.bit.CMPBHR = 0;

EPwm1Regs.TBPHS.all = 0;

EPwm1Regs.TBCTR = 0;

// Setup TBCLK

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//TB_COUNT_UPDOWN TB_COUNT_UP; // Select up-down count mode

EPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; // TB_ENABLE TB_DISABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm1Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // pass on

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm1Regs.TBCTL.bit.FREE_SOFT = 11;

//TBPRD is loaded from its shadow register on Counter = 0 event (CTR_zero)

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;//CC_CTR_ZERO_PRD;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;//CC_CTR_ZERO_PRD;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET; //���������ظ߾���Ϊ�½��ظ߾���

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; //���������ظ߾���Ϊ�½��ظ߾���

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

/// EPwm1Regs.AQSFRC.bit.RLDCSF = 3; //AQCSFRC Active Register Reload immediately

//Setup Deadband

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

/// EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

/// EPwm1Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

/// EPwm1Regs.DBRED = DC_DB_TIME_300NS;//DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero & PRD event

EPwm1Regs.ETSEL.bit.INTEN = 1; // Disable INT

EPwm1Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

// EALLOW;

// EPwm1Regs.HRCNFG.all = 0x0;

// EPwm1Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; //HR_CTR_ZERO_PRD load COMPAHR on CTR = 0 and CTR = TBPRD;HR_CTR_ZERO_PRD

// EPwm1Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm1Regs.HRCNFG.bit.EDGMODE = HR_BEP; // MEP control on both edges

// EPwm1Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm1Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm1Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

///// SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

///// EPwm1Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

// EDIS;

}

void InitEPwm2(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM2 config config for PWM2A/2B

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm2Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm2Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm2Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm2Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm2Regs.CMPB.bit.CMPBHR = 0;

EPwm2Regs.TBPHS.all = 0;

EPwm2Regs.TBCTR = 0;

// Setup TBCLK

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//TB_COUNT_UPDOWN TB_COUNT_UP; // Select up-down count mode

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // TB_ENABLE TB_DISABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm2Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // Pass on

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm2Regs.TBCTL.bit.FREE_SOFT = 11;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Set actions

EPwm2Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBU = AQ_SET;

/// EPwm2Regs.AQSFRC.bit.RLDCSF = 3; //AQCSFRC Active Register Reload immediately

// Active Low PWMs - Setup Deadband

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

// EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

// EPwm2Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

// EPwm2Regs.DBRED = DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm2Regs.ETSEL.bit.INTSEL = ET_CTR_PRD; // Select INT on Zero event

EPwm2Regs.ETSEL.bit.INTEN = 0; // Disable INT

EPwm2Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

// EALLOW;

// EPwm2Regs.HRCNFG.all = 0x0;

// EPwm2Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; // load on CTR = 0 and CTR = TBPRD

// EPwm2Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm2Regs.HRCNFG.bit.EDGMODE = HR_BEP; // MEP control on both edges

// EPwm2Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm2Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm2Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

///// EPwm2Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

//// SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

// EDIS;

}

void InitEPwm3(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM3 config config for PWM2A/2B

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm3Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm3Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm3Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm3Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm3Regs.CMPB.bit.CMPBHR = 0;

EPwm3Regs.TBPHS.all = 0;

EPwm3Regs.TBCTR = 0;

// Setup TBCLK

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Select up-down count mode

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE; //TB_ENABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm3Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync (=120 deg)

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // TB_SYNC_DISABLE TB_SYNC_IN

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm3Regs.TBCTL.bit.FREE_SOFT = 11;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Set actions

EPwm3Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm3Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CBU = AQ_SET;

/// EPwm3Regs.AQSFRC.bit.RLDCSF = 3; //AQCSFRC Active Register Reload immediately

// Active Low PWMs - Setup Deadband

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

/// EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

/// EPwm3Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

/// EPwm3Regs.DBRED = DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm3Regs.ETSEL.bit.INTSEL = ET_CTR_PRD; // Select INT on Prd event

EPwm3Regs.ETSEL.bit.INTEN = 0; // Disable INT

EPwm3Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

// EALLOW;

// EPwm3Regs.HRCNFG.all = 0x0;

// EPwm3Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; // load on CTR = 0 and CTR = TBPRD

// EPwm3Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm3Regs.HRCNFG.bit.EDGMODE = HR_FEP;///HR_BEP; // MEP control on both edges

// EPwm3Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm3Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm3Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

//// EPwm3Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

//// SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

// EDIS;

}

void InitEPwm4(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM4 config config for PWM2A/2B

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm4Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm4Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm4Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm4Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm4Regs.CMPB.bit.CMPBHR = 0;

EPwm4Regs.TBPHS.all = 0;

EPwm4Regs.TBCTR = 0;

// Setup TBCLK

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Select up-down count mode

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; //TB_DISABLE TB_ENABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm4Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync (=120 deg)

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // TB_SYNC_DISABLE TB_SYNC_IN

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm4Regs.TBCTL.bit.FREE_SOFT = 11;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

// Set actions

EPwm4Regs.AQCTLA.bit.CAD = AQ_SET; // PWM toggle high/low

EPwm4Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.CBU = AQ_SET;

/// EPwm4Regs.AQSFRC.bit.RLDCSF = 3; //AQCSFRC Active Register Reload immediately

// Active Low PWMs - Setup Deadband

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

/// EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

/// EPwm4Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

/// EPwm4Regs.DBRED = DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_PRD; // Select INT on Prd event

EPwm4Regs.ETSEL.bit.INTEN = 0;// Disable INT

EPwm4Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

// EALLOW;

// EPwm4Regs.HRCNFG.all = 0x0;

// EPwm4Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; // load on CTR = 0 and CTR = TBPRD

// EPwm4Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm4Regs.HRCNFG.bit.EDGMODE = HR_FEP;///HR_BEP; // MEP control on both edges

// EPwm4Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm4Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm4Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

///// EPwm4Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

//

// ///SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

// EDIS;

}

void InitEPwm5(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM5 config config for PWM2A/2B

EPwm5Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm5Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm5Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm5Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm5Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm5Regs.CMPB.bit.CMPBHR = 0;

EPwm5Regs.TBPHS.all = 0;

EPwm5Regs.TBCTR = 0;

// Setup TBCLK

EPwm5Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm5Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm5Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm5Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV �� CLKDIV)

EPwm5Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm5Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // PWM5ͬ��

EPwm5Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm5Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm5Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm5Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;

EPwm5Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;

// Setup compare

// Set actions

EPwm5Regs.AQCTLA.bit.CAD = AQ_SET; // Set PWM5A on Zero

EPwm5Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm5Regs.AQCTLB.bit.CBD = AQ_CLEAR; // Set PWM5A on Zero

EPwm5Regs.AQCTLB.bit.CBU = AQ_SET;

// Active Low PWMs - Setup Deadband

EPwm5Regs.DBCTL.bit.OUT_MODE = DB_DISABLE; //����������

//EPwm5Regs.DBCTL.bit.POLSEL = DB_ACTV_LO;

//EPwm5Regs.DBCTL.bit.IN_MODE = DBA_ALL;

//EPwm5Regs.DBRED = EPWM1_MIN_DB;

// EPwm5Regs.DBFED = EPWM1_MIN_DB;

//EPwm5_DB_Direction = DB_UP;

// Interrupt where we will change the Deadband

EPwm5Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Prd event

EPwm5Regs.ETSEL.bit.INTEN = 1; // Enable INT

EPwm5Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

//ADC trigger source

/*

EPwm5Regs.ETSEL.bit.SOCAEN = 1;//ʹ��ADC����ת������ // Enable SOC on A group

EPwm5Regs.ETSEL.bit.SOCASEL = 4;//�����������ӵ�CMPAʱʹ���¼� // Select SOC from from CPMA on upcount

EPwm5Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

*/

}

void InitEPwm6(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM6 config config for PWM2A/2B

EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm6Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm6Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm5Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm6Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_MIN_CMPA;

EPwm6Regs.CMPB.bit.CMPBHR = 0;

EPwm6Regs.TBPHS.all = 0;

EPwm6Regs.TBCTR = 0;

// Setup TBCLK

EPwm6Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up

EPwm6Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm6Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm6Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV �� CLKDIV)

EPwm6Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // PWM6ͬ��

EPwm6Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm6Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // Load registers every ZERO

EPwm6Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm6Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO_PRD;

EPwm6Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO_PRD;

// Set actions

EPwm6Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm6Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm6Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm6Regs.AQCTLB.bit.CBU = AQ_SET;

// Active Low PWMs - Setup Deadband

EPwm6Regs.DBCTL.bit.OUT_MODE = DB_DISABLE; //����������

EPwm6Regs.DBCTL.bit.POLSEL = DB_ACTV_LO;

//EPwm6Regs.DBCTL.bit.IN_MODE = DBA_ALL;

//EPwm6Regs.DBRED = EPWM1_MIN_DB;

//EPwm6Regs.DBFED = EPWM1_MIN_DB;

// EPwm6_DB_Direction = DB_UP;

// Interrupt where we will change the Deadband

// EPwm6Regs.ETSEL.bit.INTSEL = ET_CTR_PRD; // Select INT on Prd event

// EPwm6Regs.ETSEL.bit.INTEN = 1; // Enable INT

// EPwm6Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

//ADC trigger source

// EPwm6Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group

// EPwm6Regs.ETSEL.bit.SOCASEL = 1; // Select SOC from from CPMA on downcount

// EPwm6Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

// EALLOW;

// CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Disable TBCLK within the EPWM

// EDIS;

}

void InitEPwm7(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM2 config config for PWM2A/2B

EPwm7Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm7Regs.TBPRD = EPWM_AD_TIMER_TBPRD; // (100M/100k-1)=999 Set timer period-100kHz,PWM frequency = 1/(2*TBPRD)

EPwm7Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm7Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm7Regs.CMPB.bit.CMPB = EPWM1_TIMER_TBPRD - EPWM1_TIMER_TBPRD;

EPwm7Regs.CMPB.bit.CMPBHR = 0;

EPwm7Regs.TBPHS.all = 0;

EPwm7Regs.TBCTR = 0;

// Setup TBCLK

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//TB_COUNT_UPDOWN TB_COUNT_UP; // Select up-down count mode

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE; // TB_ENABLE TB_DISABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm7Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // pass on

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm7Regs.TBCTL.bit.FREE_SOFT = 11;

//TBPRD is loaded from its shadow register on Counter = 0 event (CTR_zero)

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;//CC_CTR_ZERO_PRD;

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;//CC_CTR_ZERO_PRD;

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm7Regs.AQCTLA.bit.CAD = AQ_SET; //���������ظ߾���Ϊ�½��ظ߾���

EPwm7Regs.AQCTLA.bit.CAU = AQ_CLEAR; //���������ظ߾���Ϊ�½��ظ߾���

/// EPwm1Regs.AQSFRC.bit.RLDCSF = 3; //AQCSFRC Active Register Reload immediately

//Setup Deadband

EPwm7Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

/// EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

/// EPwm1Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

/// EPwm1Regs.DBRED = DC_DB_TIME_300NS;//DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm7Regs.ETSEL.bit.INTSEL = 0; // Select INT on Zero & PRD event

EPwm7Regs.ETSEL.bit.INTEN = 0; // Disable INT

EPwm7Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

EPwm7Regs.ETSEL.bit.SOCAEN = 1; //Eables SOCA pulse

EPwm7Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO;//20121008//ET_CTR_PRD;//ET_CTR_ZERO; //Enable CNTR = zero event

EPwm7Regs.ETPS.bit.SOCAPRD = ET_1ST; // Generate pulse on 1st event

// EALLOW;

// EPwm7Regs.HRCNFG.all = 0x0;

// EPwm7Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; //HR_CTR_ZERO_PRD load COMPAHR on CTR = 0 and CTR = TBPRD;HR_CTR_ZERO_PRD

// EPwm7Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm7Regs.HRCNFG.bit.EDGMODE = HR_BEP; // MEP control on both edges

// EPwm7Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm7Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm7Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

///// SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

///// EPwm1Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

//

// EDIS;

}

void InitEPwm8(void)

{

// ePWM channel register configuration with HRPWM

// ePWMxA toggle low/high with MEP control on Rising edge

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

///EPWM8 config config for PWM2A/2B

EPwm8Regs.TBCTL.bit.PRDLD = TB_SHADOW; // set Shadow load

EPwm8Regs.TBPRD = EPWM1_TIMER_TBPRD; // (60M/250k-1)=239 Set timer period-120kHz,PWM frequency = 1/(2*TBPRD)

EPwm8Regs.CMPA.bit.CMPA = EPWM1_MIN_CMPA;

EPwm8Regs.CMPA.bit.CMPAHR = 0; // initialize HRPWM extension

EPwm8Regs.CMPB.bit.CMPB = 0x3E7;

//EPwm8Regs.CMPB.bit.CMPBHR = 0;

EPwm8Regs.TBPHS.all = 0;

EPwm8Regs.TBCTR = 0;

// Setup TBCLK

EPwm8Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//TB_COUNT_UPDOWN TB_COUNT_UP; // Select up-down count mode

EPwm8Regs.TBCTL.bit.PHSEN = TB_ENABLE; // TB_ENABLE TB_DISABLE: TBCTR phase load on SYNC (required for updown count HR control

EPwm8Regs.TBCTL.bit.PHSDIR = TB_UP; // Count TB_UP on sync

EPwm8Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // pass on

EPwm8Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm8Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT / (HSPCLKDIV CLKDIV)

EPwm8Regs.TBCTL.bit.FREE_SOFT = 11;

//TBPRD is loaded from its shadow register on Counter = 0 event (CTR_zero)

EPwm8Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;//CC_CTR_ZERO_PRD;

EPwm8Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;//CC_CTR_ZERO_PRD;

EPwm8Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm8Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm8Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm8Regs.AQCTLB.bit.CBU = AQ_CLEAR;

//Setup Deadband

EPwm8Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;///DBB_ENABLE;//S1=1,S0=0

/// EPwm8Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;//S3=0,S2=0

/// EPwm8Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;//S5=1,S4=0

/// EPwm8Regs.DBRED = DC_DB_TIME_300NS;//DC_DB_TIME_300NS;

// Interrupt where we will change the Deadband

EPwm8Regs.ETSEL.bit.INTSEL = 0; // Select INT on Zero & PRD event

EPwm8Regs.ETSEL.bit.INTEN = 0; // Disable INT

EPwm8Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 1st event

// EALLOW;

// EPwm8Regs.HRCNFG.all = 0x0;

// EPwm8Regs.HRCNFG.bit.HRLOAD = HR_CTR_ZERO_PRD; //HR_CTR_ZERO_PRD load COMPAHR on CTR = 0 and CTR = TBPRD;HR_CTR_ZERO_PRD

// EPwm8Regs.HRCNFG.bit.AUTOCONV = 1; // Enable autoconversion for HR period

// EPwm8Regs.HRCNFG.bit.EDGMODE = HR_BEP; // MEP control on both edges

// EPwm8Regs.HRCNFG.bit.CTLMODE = HR_CMP; // CMPAHR and TBPRDHR HR control

//

// EPwm8Regs.HRPCTL.bit.TBPHSHRLOADE = 1; // Enable TBPHSHR sync (required for updwn count HR control)

// EPwm8Regs.HRPCTL.bit.HRPE = 1; // Turn on high-resolution period control.

//

///// SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

///// EPwm1Regs.TBCTL.bit.SWFSYNC = 1; // Synchronize high resolution phase to start HR period

//

// EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Disable TBCLK within the EPWM

EDIS;

}

//===========================================================================

// End of file.

//===========================================================================