如题

EPWM触发ADC采样,我希望通过Timer0来控制EPWM的freeze/un-freeze,也就是在Timer0中断进行时,关闭EPWM,不生成event trigger,不允许ADC采样,当Timer0中断结束时,再打开EPWM,开始ADC采样.

但是采样到的结果会发生变化,在打开EPWM后,ADC采样的结果会略高于上一次采样的值.请问是什么原因,怎么避免.

ps: 我的设计是,利用28377D的CLA处理ADC采样,经过160次采样后,Timer0中断发生,进行一次控制,并修改参数,但是实际的系统根据Timer0的周期频率,并不能准确的在160次时进入中断,在Timer0中断时,CLA依然处理ADC采样,待Timer0中断后,执行一次CLA中断,然后继续CLA处理并中断.这部分的数据会打乱我的数据,我希望能去掉,所以在Timer0中断中加入了开关ADC采样,并清除了CLA中断,重置了CLA的数据然后开始新一轮的循环.

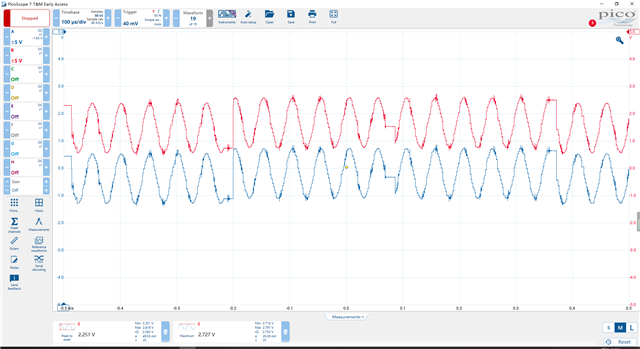

如图是我用DAC输出了ADC采样的结果,中间信号中断的部分是进行了Timer0中断,DAC未更新输出,当Timer0中断后,重新开始采样时,信号的峰值会与前次采样的峰值不等,略高或略低,会不会是因为开关了EPWM/ADC导致采样结果的不正确