测试时发现cmpss保护误触发,实际电压仅有1.9V,将相应引脚(8脚)接地后仍然触发保护,可能是什么原因导致的

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,有确认过是否确实是由CMPSS触发的误保护?或者会不会引脚有干扰导致保护被触发?

目前的信息来看没办法判定具体问题是什么引起的。

这样的话可能需要你附上CMPSS部分的代码,目前的信息看不出是什么原因。

void InitComp(void)

{

/* set up the GPIO and X-BAR input configurations before enabling the TZ*/

EPwm1Regs.TZSEL.all = 0x0;

EPwm2Regs.TZSEL.all = 0x0;

/* Initialize Analog Subsystem */

EALLOW;

AnalogSubsysRegs.CMPHPMXSEL.bit.CMP1HPMXSEL = 1; // Bits to select one of the many sources on CopmHP inputs. Refer to Pimux diagram for details.

EDIS;

/* Initialize Comparators */

EALLOW;

//Cmpss1Regs.COMPCTL.all = 0x9414;

Cmpss1Regs.COMPCTL.bit.COMPHSOURCE = 0; // 0 High Comparator Source Select

Cmpss1Regs.COMPCTL.bit.COMPHINV = 0; // 1 High Comparator Invert Select

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = 1; // 3:2 High Comparator Trip Select

Cmpss1Regs.COMPCTL.bit.CTRIPOUTHSEL = 1; // 5:4 High Comparator Trip Output Select

Cmpss1Regs.COMPCTL.bit.ASYNCHEN = 0; // 6 High Comparator Asynchronous Path Enable

Cmpss1Regs.COMPCTL.bit.COMPLSOURCE = 0; // 8 Low Comparator Source Select

Cmpss1Regs.COMPCTL.bit.COMPLINV = 0; // 9 Low Comparator Invert Select

Cmpss1Regs.COMPCTL.bit.CTRIPLSEL = 1; // 11:10 Low Comparator Trip Select

Cmpss1Regs.COMPCTL.bit.CTRIPOUTLSEL = 1; // 13:12 Low Comparator Trip Output Select

Cmpss1Regs.COMPCTL.bit.ASYNCLEN = 0; // 14 Low Comparator Asynchronous Path Enable

Cmpss1Regs.COMPCTL.bit.COMPDACE = 1; // 15 Comparator/DAC Enable

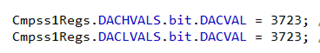

Cmpss1Regs.DACHVALS.bit.DACVAL = 3723; // 20A / #define ADC_CURRENT_BUSIN_OC_FIXED_COEFF (0.0052882)

Cmpss1Regs.DACLVALS.bit.DACVAL = 3723; // 20A / #define ADC_CURRENT_BUSIN_OC_FIXED_COEFF (0.0052882)

//Cmpss1Regs.COMPLOCK.all = 0x000F;

Cmpss1Regs.COMPLOCK.bit.COMPCTL = 1; // 0 COMPCTL Lock

Cmpss1Regs.COMPLOCK.bit.COMPHYSCTL = 1; // 1 COMPHYSCTL Lock

Cmpss1Regs.COMPLOCK.bit.DACCTL = 1; // 2 DACCTL Lock

Cmpss1Regs.COMPLOCK.bit.CTRIP = 1; // 3 CTRIP Lock

EDIS;

/* Initialize EPwmXbarRegs */

EALLOW;

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX0 = 0; // 1:0 Mux0 Configuration for TRIP4 of EPWM-XBAR

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX0 = 1; // ePWM XBAR Mux Enable for TRIP4

EPwmXbarRegs.TRIPOUTINV.bit.TRIP4 = 0; // ePWM XBAR Output Inversion Register

EDIS;

/* Initialize DC */

EALLOW;

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_TRIPIN4; // 3:0 Digital Compare A High COMP Input Select

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_TRIPIN4; // 11:8 Digital Compare B High COMP Input Select

EPwm1Regs.DCACTL.bit.EVT2SRCSEL = DC_EVT2; // 8 DCAEVT2 Source Signal

EPwm1Regs.DCACTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC; // 9 DCAEVT2 Force Sync Signal

EPwm2Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_TRIPIN4; // 3:0 Digital Compare A High COMP Input Select

EPwm2Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_TRIPIN4; // 11:8 Digital Compare B High COMP Input Select

EPwm2Regs.DCACTL.bit.EVT2SRCSEL = DC_EVT2; // 8 DCAEVT2 Source Signal

EPwm2Regs.DCACTL.bit.EVT2FRCSYNCSEL = DC_EVT_ASYNC; // 9 DCAEVT2 Force Sync Signal

EDIS;

/* Initialize TZ */

EALLOW;

EPwm1Regs.TZDCSEL.bit.DCAEVT2 = TZ_DCAH_HI; // 5:3 Digital Compare Output A Event 2

EPwm1Regs.TZSEL.bit.DCAEVT2 = 1; // 6 DCAEVT2 CBC select

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // 1:0 TZ1 to TZ6 Trip Action On EPWMxA

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // 3:2 TZ1 to TZ6 Trip Action On EPWMxB

EPwm1Regs.TZCLR.all = 0xFFFF; // Trip Zone Clear Register

EPwm2Regs.TZDCSEL.bit.DCAEVT2 = TZ_DCAH_HI; // 5:3 Digital Compare Output A Event 2

EPwm2Regs.TZSEL.bit.DCAEVT2 = 1; // 6 DCAEVT2 CBC select

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // 1:0 TZ1 to TZ6 Trip Action On EPWMxA

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // 3:2 TZ1 to TZ6 Trip Action On EPWMxB

EPwm2Regs.TZCLR.all = 0xFFFF; // Trip Zone Clear Register

EDIS;

你的代码中只配置了:

EALLOW; AnalogSubsysRegs.CMPHPMXSEL.bit.CMP1HPMXSEL = 1; // Bits to select one of the many sources on CopmHP inputs. Refer to Pimux diagram for details. EDIS;

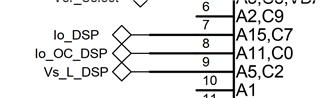

CMP1LPMXSEL 没有被配置。 COMPL 是随机跳闸的吗?