在这颗芯片的例程中,没有看到作为I2C从机的程序,我想要一个参考程序,满足以下要求:

1. 从机,8位数据。

2. 能中断响应I2C。

3. 对主机而言,这颗芯片在收到地址后能进入中断,在接收和发送一个数据后,也能进入中断。

麻烦提供一个参考程序,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在这颗芯片的例程中,没有看到作为I2C从机的程序,我想要一个参考程序,满足以下要求:

1. 从机,8位数据。

2. 能中断响应I2C。

3. 对主机而言,这颗芯片在收到地址后能进入中断,在接收和发送一个数据后,也能进入中断。

麻烦提供一个参考程序,谢谢!

你好,非常抱歉,目前官方还没有I2C作为从机的程序,包括其他芯片也没有提供类似要求的例程。

你可以找一下第三方网页上是否有相关例程

谢谢Green的回复!

如果没有参考例程,可否帮忙看看以下程序哪里有问题?谢谢!

初始化代码:

{

// Initialize I2C-A:

EALLOW;

SysCtrlRegs.PCLKCR0.bit.I2CAENCLK = 1; // I2C

GpioCtrlRegs.GPBPUD.bit.GPIO32 = 0; // Enable pull-up for GPIO32 (SDAA)

GpioCtrlRegs.GPBPUD.bit.GPIO33 = 0; // Enable pull-up for GPIO33 (SCLA)

GpioCtrlRegs.GPBQSEL1.bit.GPIO32 = 3; // Asynch input GPIO32 (SDAA)

GpioCtrlRegs.GPBQSEL1.bit.GPIO33 = 3; // Asynch input GPIO33 (SCLA)

GpioCtrlRegs.GPBMUX1.bit.GPIO32 = 1; // Configure GPIO32 for SDAA operation

GpioCtrlRegs.GPBMUX1.bit.GPIO33 = 1; // Configure GPIO33 for SCLA operation

EDIS;

I2caRegs.I2CMDR.bit.IRS = 0; //I2C Reset bit.

I2caRegs.I2CMDR.bit.MST = 0; //@NOTE: 0=slave mode; 1=master mode.

I2caRegs.I2CMDR.bit.XA = 0; //@NOTE: 0=7bit address; 1=10bit address.

I2caRegs.I2CMDR.bit.BC = 0x00; //@NOTE: 0=8 bits per data byte

I2caRegs.I2CMDR.bit.NACKMOD = 0; //I2C Reset bit.

I2caRegs.I2CEMDR.bit.BCM = 0x00;

I2C_SetPMbusAddress(SLAVE_ADDRESS_INIT);

I2caRegs.I2CIER.bit.AAS = 1; //Addressed as slave interrupt enable 1h (R/W) = Interrupt request enabled

I2caRegs.I2CIER.bit.SCD = 1; //Stop condition detected interrupt enable 1h (R/W) = Interrupt request enabled

//this for non-PEC check

I2caRegs.I2CIER.bit.RRDY = 1; //receive ready

I2caRegs.I2CIER.bit.XRDY = 1; //transmit ready

I2caRegs.I2CSAR = 0x0000; // The next address.

I2caRegs.I2CPSC.bit.IPSC = 5; // Prescaler - need 7-12 Mhz on module clk (60/6 = 10MHz)

// module clock frequency = I2C input clock frequency/(IPSC + 1)

// 10MHz/(45+5 + 45 +5) = 100K

I2caRegs.I2CCLKL = 45; // NOTE: must be non zero

I2caRegs.I2CCLKH = 45; // NOTE: must be non zero

I2caRegs.I2CMDR.bit.IRS = 1; //I2C Reset bit. Take I2C out of reset

I2caRegs.I2CFFTX.all = 0x0000; // Enable FIFO mode and TXFIFO

I2caRegs.I2CFFRX.all = 0x0000; // Enable RXFIFO, clear RXFFINT,

}

中断处理代码:

{

Uint16 u16IntSrcReg;

// static Uint16 i = 0;

// static Uint16 j = 0;

u16IntSrcReg = (Uint16)I2caRegs.I2CISRC.bit.INTCODE;

switch(u16IntSrcReg)

{

case 0x01:

//Arbitration lost

break;

case 0x02:

//No-acknowledgment condition detected

break;

case 0x03:

//Registers ready to be accessed

break;

case 0x04:

//while(I2caRegs.I2CFFRX.bit.RXFFST < 4) {};

j= 0;

if(I2caRegs.I2CSTR.bit.SDIR == 1)

{

//

}

else//slave read data

{

RxData[i] = I2caRegs.I2CDRR;

command = RxData[0];

if(i>=6)

{

i=0;

}

else

{

i++;

if((command_type == 1)&&(command == 0x99))//command length =1

{

i=0;

}

}

}

break;

case 0x05://Transmit data ready

if(command == 0x99)

{

//while(!I2C_xrdy());

//while(I2caRegs.I2CSTR.bit.XRDY != 1) {};// 1 = Data transferred tp the core TX register after shifting data

if(j>=7)

{

I2caRegs.I2CDXR = 0xFF;

}

else

{

I2caRegs.I2CDXR = Array[j];

}

j++;

}

else

{

I2caRegs.I2CDXR = 0xFF;

}

break;

case 0x06:

//Stop condition detected

break;

case 0x07:

//Addressed as slave

if(I2caRegs.I2CSTR.bit.SDIR == 1) //means address read

{

//address read

I2C_bIsSlaveAddressRead();

}

else

{

//I2caRegs.I2CIER.bit.XRDY = 0;//address write

//I2caRegs.I2CMDR.bit.TRX = 0;

I2C_bIsSlaveAddressWrite();

//i=0;

}

break;

default:

//error happen

break;

}

PieCtrlRegs.PIEACK.all = PIEACK_GROUP8; //release other interrupt

}

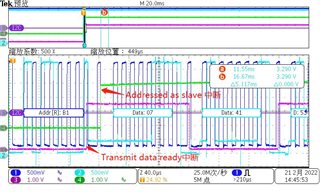

问题:怎样设定,可以让地址中断先发生,而数据发送中断后发生?谢谢!

这个很抱歉,我对I2C模块也不太熟悉。建议你将问题直接发布到英文E2E论坛,英文论坛应该会有对I2C比较熟悉的工程师帮你解决问题: