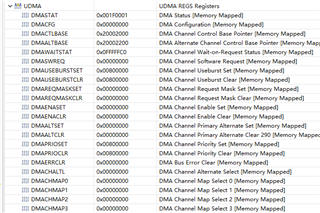

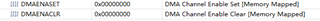

原来uart收发采用中断的方式实现,嫌中断太频繁,现在想改dma,使用的串口1,用的是udma_demo,只开了uart发送的dma,接收部分以及ram to ram部分注释掉了,我理解udma配置好了,通道使能就可以发送了,需要其他操作吧,使能部分我尝试读了,都是faulse

代码flash运行,管脚配置正确,时钟都正确*(单测试串口发送可以用测试代码发送数据到上位机显示。)

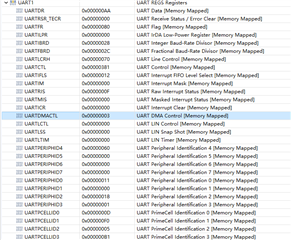

大致过程参考了demo,同时对着spru22i手册查看了16.4.3部分寄存器的设置,

代码 如下:

void UART1IntHandler(void)

{

unsigned long ulStatus;

ulStatus = UARTIntStatus(UART1_BASE, 1);

UARTIntClear(UART1_BASE, ulStatus);

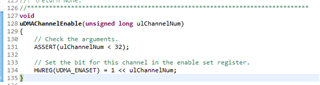

if(!uDMAChannelIsEnabled(UDMA_CHANNEL_UART1TX))

{

uDMAChannelTransferSet(UDMA_CHANNEL_UART1TX | UDMA_PRI_SELECT,

UDMA_MODE_BASIC, g_ucTxBuf,

(void *)(UART1_BASE + UART_O_DR),

sizeof(g_ucTxBuf));

// The uDMA TX channel must be re-enabled.

uDMAChannelEnable(UDMA_CHANNEL_UART1TX);

/////// 怎么读都是没有使能

// uDMAChannelIsEnabled(UDMA_CHANNEL_UART1TX);

}

}

//*****************************************************************************

void

InitUART1Transfer(void)

{

unsigned int uIdx;

for(uIdx = 0; uIdx < UART_TXBUF_SIZE; uIdx++)

{

g_ucTxBuf[uIdx] = uIdx;

}

SysCtlPeripheralEnable(SYSCTL_PERIPH_UART1);

SysCtlPeripheralSleepEnable(SYSCTL_PERIPH_UART1);

UARTConfigSetExpClk(UART1_BASE, SysCtlClockGet(SYSTEM_CLOCK_SPEED), 115200,

UART_CONFIG_WLEN_8 | UART_CONFIG_STOP_ONE |

UART_CONFIG_PAR_NONE);

UARTFIFOLevelSet(UART1_BASE, UART_FIFO_TX4_8, UART_FIFO_RX4_8);

UARTEnable(UART1_BASE);

UARTDMAEnable(UART1_BASE, UART_DMA_TX);

IntEnable(INT_UART1);

uDMAChannelAttributeDisable(UDMA_CHANNEL_UART1TX,

UDMA_ATTR_ALTSELECT |

UDMA_ATTR_HIGH_PRIORITY | UDMA_ATTR_REQMASK);

uDMAChannelAttributeEnable(UDMA_CHANNEL_UART1TX, UDMA_ATTR_USEBURST);

uDMAChannelControlSet(UDMA_CHANNEL_UART1TX | UDMA_PRI_SELECT,

UDMA_SIZE_8 | UDMA_SRC_INC_8 | UDMA_DST_INC_NONE |

UDMA_ARB_4);

uDMAChannelTransferSet(UDMA_CHANNEL_UART1TX | UDMA_PRI_SELECT,

UDMA_MODE_BASIC, g_ucTxBuf,

(void *)(UART1_BASE + UART_O_DR),

sizeof(g_ucTxBuf));

////测试串口配置,管脚是否正确,能接到计算机上正常收到数据

// UARTCharPutNonBlocking(UART1_BASE,0xaa);

// UARTCharPutNonBlocking(UART1_BASE,0xaa);

// UARTCharPutNonBlocking(UART1_BASE,0xaa);

// UARTCharPutNonBlocking(UART1_BASE,0xaa);

// UARTCharPutNonBlocking(UART1_BASE,0xaa);

uDMAChannelEnable(UDMA_CHANNEL_UART1TX);

}

int main(void)

{

HWREG(SYSCTL_MWRALLOW) = 0xA5A5A5A5;

// Sets up PLL, M3 running at 75MHz and C28 running at 150MHz

SysCtlClockConfigSet(SYSCTL_USE_PLL | (SYSCTL_SPLLIMULT_M & 0xF) |

SYSCTL_SYSDIV_1 | SYSCTL_M3SSDIV_2 |

SYSCTL_XCLKDIV_4);

#ifdef _FLASH

memcpy(&RamfuncsRunStart, &RamfuncsLoadStart, (size_t)&RamfuncsLoadSize);

FlashInit();

#endif

////配置管脚

PinoutSet();

// Disable clock supply for the watchdog modules

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG1);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG0);

// Unlock the register to change the commit register value for Port B Pin 7

// This disables the NMI functionality on the pin and allows other muxing

// options to be used

HWREG(GPIO_PORTB_BASE+GPIO_O_LOCK) = GPIO_LOCK_KEY_DD;

// Write to commit register

HWREG(GPIO_PORTB_BASE+GPIO_O_CR) |= 0x000000FF;

// Delay

for (i=0;i<20;i++){};

// Enable peripherals to operate when CPU is in sleep.

SysCtlPeripheralClockGating(true);

// Register interrupt handlers in the RAM vector table

IntRegister(INT_UART1, UART1IntHandler);

// Enable the uDMA controller at the system level. Enable it to continue

// to run while the processor is in sleep.

SysCtlPeripheralEnable(SYSCTL_PERIPH_UDMA);

SysCtlPeripheralSleepEnable(SYSCTL_PERIPH_UDMA);

// Enable the uDMA controller error interrupt. This interrupt will occur

// if there is a bus error during a transfer.

IntEnable(INT_UDMAERR);

// Enable the uDMA controller.

uDMAEnable();

// Point at the control table to use for channel control structures.

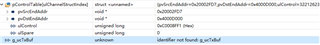

uDMAControlBaseSet(ucControlTable);

// Initialize the uDMA UART transfers.

InitUART1Transfer();

// Loop until the button is pressed. The processor is put to sleep

// in this loop so that CPU utilization can be measured.

while(1)

{

;

}