我用测试C28核和CLA并行处理时(进行同样的代码),发现软件采用CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_1)启动TASK1时,并没有立即进入CLA_tas(),延时了1us才进入task。

__interrupt void Cla1Task1 ( void )

{

//

//Local Variables

//

// num = 0;

GPIO_writePin(78,1);

// GpioDataRegs.GPBSET.bit.GPIO33 = 1;

int xTblIdx; //integer valued Table index

float A0,A1,A2; //Table coefficients

float *entry;

float result;

int i;

//

//Preprocessing

//

//__mdebugstop();

xTblIdx = fVal * TABLE_SIZE_M_1; //convert table index to u16-bits

xTblIdx = xTblIdx * 3; //Table is ordered as 3 32-bit coefficients, the

//index points to these triplets, hence the *3*sizeof(float)

// entry = &CLAasinTable[xTblIdx];

// A0 = *entry++;

// A1 = *entry++;

// A2 = *entry;

// result = A0 + fVal*(A1 + A2*fVal);

//

// //

// //Post processing

// //

// if(fVal < 0)

// {

// result = - result;

// }

xTblIdx = xTblIdx * 3333;

xTblIdx = xTblIdx * 3234 + xTblIdx * 367 ;

fResult = xTblIdx;

// GpioDataRegs.GPBCLEAR.bit.GPIO33 = 1;

GPIO_writePin(78,0);

}void main(void)

{

//

// Intialize device clock and peripherals

//

Device_init();

//

// Initialize GPIO and configure the GPIO pin as a push-pull output

//

GPIO_setPadConfig(78, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_78_GPIO78);

GPIO_setDirectionMode(78, GPIO_DIR_MODE_OUT);

GPIO_setMasterCore(78, GPIO_CORE_CPU1_CLA1);

GPIO_setDirectionMode(80, GPIO_DIR_MODE_OUT);

GPIO_setPinConfig(80);

//

// Disable pin locks and enable internal pullups.

//

//Device_initGPIO(); //skipped for this example

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Configure the CLA memory spaces first followed by

// the CLA task vectors

//

CLA_configClaMemory();

CLA_initCpu1Cla1();

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

//

// Run the test

//

//CLA_runTest();

for(;;)

{

int xTblIdx1; //integer valued Table index

float result1;

int i;

GPIO_writePin(80,1);

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_1);

xTblIdx1 = fVal * TABLE_SIZE_M_1; //convert table index to u16-bits

xTblIdx1 = xTblIdx1 * 3; //Table is ordered as 3 32-bit coefficients, the

//index points to these triplets, hence the *3*sizeof(float)

xTblIdx1 = xTblIdx1 * 3333;

xTblIdx1 = xTblIdx1 * 3234 + xTblIdx1 * 367 ;

fResult = xTblIdx1;

GPIO_writePin(80,0);

DEVICE_DELAY_US(50);

}

}

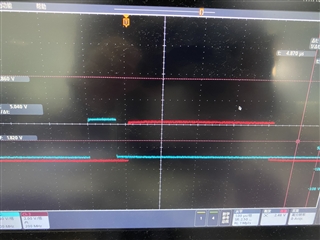

测试发现GPIO78引脚都是再GPIO80拉高后1us才被拉高,而且主函数执行时间才750ns,而CLA执行了4.2us,

蓝色为CPIO80,红色为GPIO78.

按我的理解,CLA跟CPU应该是并行处理,触发AICK1,进入TASK1执行代码,CPU继续继续z主程序代码,然后等待task完成,但实测并没有得到这个结果。