Other Parts Discussed in Thread: CONTROLSUITE

在使用F28M36的内部ADC进行采样时,使用内部基准电压,ADC1的输入端口为ADC1INB0,ADC2的输入端口为ADC2INB1。发现ADC1与ADC2采样得到的值均偏小,并且使用ADC2采样得到的值偏小的幅度小一些。能咨询一下,怎样解决ADC采样偏小问题,以及为何ADC1与ADC2的采样结果不一致。谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在使用F28M36的内部ADC进行采样时,使用内部基准电压,ADC1的输入端口为ADC1INB0,ADC2的输入端口为ADC2INB1。发现ADC1与ADC2采样得到的值均偏小,并且使用ADC2采样得到的值偏小的幅度小一些。能咨询一下,怎样解决ADC采样偏小问题,以及为何ADC1与ADC2的采样结果不一致。谢谢!

你好,不知道你的采样是两个通道同时采的,还是单个通道进行测试的?

另外,测试使用的是例程还是自己编写的工程?

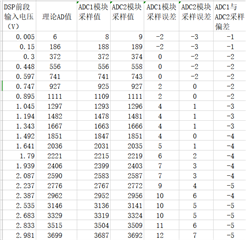

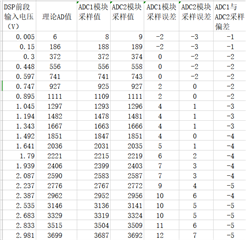

使用的是两个通道同时采的,不过程序是自己编写的程序。对于这个我也使用了controlSUITE中的例程。测试结果如下:

不过这一次测试的是ADC1的ADCINAO与ADC2的ADC2INA1的端口,使用的两个通道同时采

看到有一个说法是,如果用两路相邻的采样通道同时采样,这样会造成通道之间内部互相有分压。

如果用相隔的两个通道测试有这样的问题吗?如果确认只是相邻通道才有这个问题的话我再咨询一下有没有什么方法可以避免的

之前的测试结果是采用循环采样模式,不过信号的输入是从ADCINA0输入,芯片手册上说明ADC1的ADC1INAO与ADC2的ADC2INA1输入是连接在一起的。所以就读取了ADC1INAO与ADC2INA1的采样后的值。这种采样模式是否存在分压?

你好,我咨询了一下这款芯片的专家,但是这几天隔了周末,可能要国外的下周一才能回复,也就是国内的下周一晚上。我应该会在下周二工作时间将对方回复更新到这边

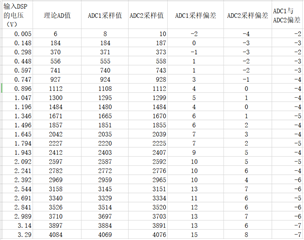

由于我们观察到的误差随着输入电压的变化而变化,这就是如下所示的gain error contribution。请注意,在满量程时,随温度变化的规格为 +/-60LSB,你观察到的值远低于两个 ADC(分别为 -15LSB 和 -7LSB)。这里也可能有一些偏移分量......

如果我对每个 ADC 使用 2pt 公式,我会得到以下结果:

ADC1 增益误差为 0.995% 或 -20LSB 偏移误差 = 3LSB

ADC2 增益误差为 0.996% 或 -16LSB 偏移误差 = -1LSB

所以,这些读数在datasheet的规格范围内,这种变化是正常的。

就 ADC 之间的差异而言,还有 +/-4LSB 的增益和偏移的ch/ch变化规范,这也满足。

可以使用与 VREFLO 的内部连接来自行校准偏移。由于这对于两个 ADC 都是相同的,因此除了本地偏移之外,还可以使用它来减少 ADC 与 ADC 的偏移。

对于本地或 ADC 之间的增益误差,如果可以对两个 ADC 有共同的参考,就可以在数学上消除增益误差,或者至少消除 ADC 之间的增量后的结果。