GPIO28配置如下:

GpioCtrlRegs.GPAPUD.bit.GPIO28 = 0; // enable Pullup

GpioCtrlRegs.GPAMUX2.bit.GPIO28 = 0; // Function as Gpio

GpioCtrlRegs.GPADIR.bit.GPIO28 = 1; // 0uput

GpioDataRegs.GPADAT.bit.GPIO28 = 0;

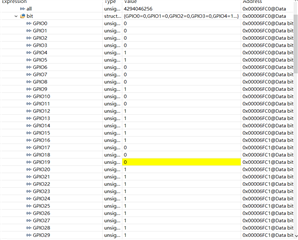

DEBUG模式下:CPU RESET后GPADAT数据寄存器状态如图所示: