Part Number: TMS320F280039C

Other Parts Discussed in Thread: C2000WARE

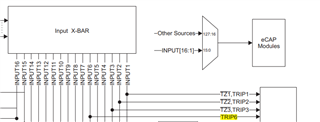

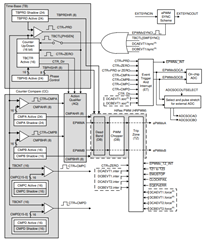

Each ePWM module is connected to six TZn signals (TZ1 to TZ6). TZ1 to TZ3 are sourced from the GPIO mux. TZ4 is sourced from an inverted EQEPxERR signal on those devices with an EQEP module. TZ5 is connected to the system clock fail logic, and TZ6 is sourced from the EMUSTOP output from the CPU. These signals indicate external fault or trip conditions, and the ePWM outputs can be programmed to respond accordingly when faults occur.

这个意思是不是说用户只能配置TZ1 - 3, TZ 1-6 是专用的,用户无法再用?