Other Parts Discussed in Thread: C2000WARE,

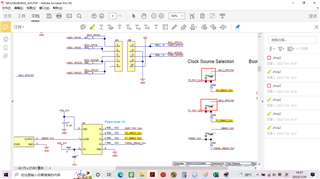

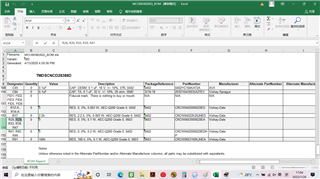

28388控制卡(RevB)上的PHY时钟部分电路如下:

从原理图上看,PHY的25MHz时钟是时钟buffer提供的,与EtherCAT PHY Clock GPIO154连接的两个0欧姆电阻没有焊接

我理解两片PHY的25MHz时钟源是时钟buffer提供的

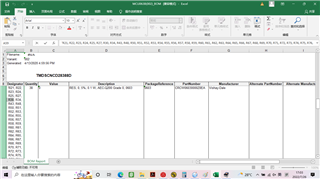

但是在BOM中,电阻R30没有标注不焊接

R29也没有标注不焊接

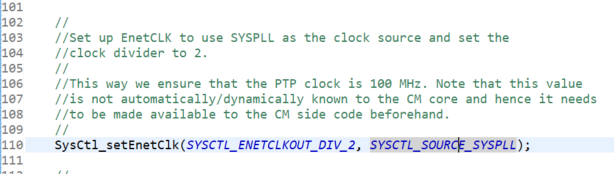

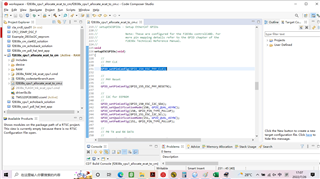

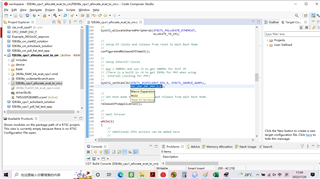

在f2838x_cpu1_allocate_ecat_to_cm及f2838x_cpu1_pdi_hal_test_app两份代码中,关于PHY时钟的配置相同,如下所示:

首先,GPIO154配置为ESC的PHY时钟输出外设功能管脚

在时钟配置时,也使能了ESC的PHY时钟输出

我是才开始用388的ESC,所以请教下大家,软件这样配置以后,PHY的25MHz时钟应该是ESC发出来的吧

但是硬件上又没有焊接GPIO154链路上的0欧姆电阻

问题1.那么,PHY的25MHz时钟源到底是谁呢?

问题2.R29和R30,在控制卡上到底焊接的是哪个呢。官网上的照片是RevA版本的,没有RevB版本控制卡正反面照片。