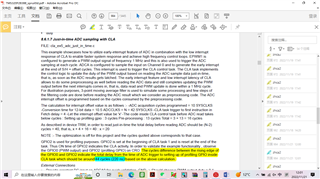

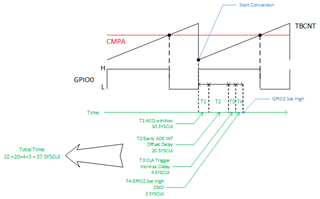

问题1. 请问GPIO0和GPIO2上升沿的延迟为什么是44个系统时钟呢,我做了如下的分析,我觉得应该是37个系统时钟,下图以第二周期为例进行分析

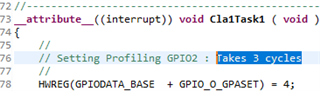

问题2.GPIO置高指令需要消耗的3个系统时钟,是如何计算出算出的

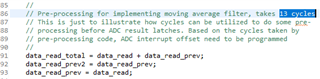

问题3.滤波处理的部分消耗的13个系统时钟是如何得知的呢?这个和问题2类似

问题4.这个例程的引用中,对时钟很敏感,如果早一个制中用CLA读取ADC数据是不是有可能失败,那是不是要求ADC中断前的预处理部分需要准确计算出消耗的时钟?再有就是如果执行过程中多一个或者少一个系统时钟是不是都会产生一定的风险?大家在用just in time的时候有什么经验可以分享一下吗?