关于IIC读取:

IIC配置如下:

GPIO_setPinConfig(GPIO_26_I2CA_SDA); // SDA, I2C-A Open-Drain Bidirectional Data

GPIO_setPadConfig(26, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(26, GPIO_QUAL_ASYNC);

GPIO_setPinConfig(GPIO_27_I2CA_SCL); // SCL, I2C-A Open-Drain Bidirectional Clock

GPIO_setPadConfig(27, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(27, GPIO_QUAL_ASYNC);

// Initialize I2C

//I2caRegs.I2CMDR.bit.IRS = 0;

I2caRegs.I2CSAR.bit.SAR = 0x50; // Set slave address

I2caRegs.I2CMDR.bit.MST = 1; // Select master or slave mode

I2caRegs.I2CMDR.bit.DLB = 0; // Enable digital loopback bit

//I2caRegs.I2CPSC.all = 10; // Prescaler - need 7-12 Mhz on module clk

I2caRegs.I2CPSC.all = 11;

//I2caRegs.I2CCLKL = 10; // NOTE: must be non zero

//I2caRegs.I2CCLKH = 5; // NOTE: must be non zero

I2caRegs.I2CCLKL = 35; // NOTE: must be non zero

I2caRegs.I2CCLKH = 35; // NOTE: must be non zero

//I2caRegs.I2CFFTX.bit.TXFFIL = 16; // Set fifo interrupt level

//I2caRegs.I2CFFRX.bit.RXFFIENA = 1; // Enable Rx Fifo interrupt

//I2caRegs.I2CFFRX.bit.RXFFIL = 16; // Set fifo interrupt level

//I2caRegs.I2CFFRX.bit.RXFFINTCLR = 1; // Clear Rx interrupt flag

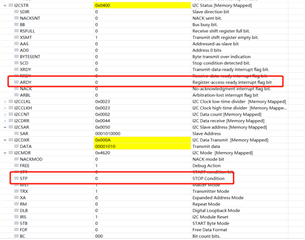

I2caRegs.I2CIER.all = 0x24; // Enable SCD & ARDY interrupts

I2caRegs.I2CFFTX.all = 0x6000; // Enable TxFIFO mode

I2caRegs.I2CFFRX.all = 0x2000; // Enable RxFIFO mode

//I2caRegs.I2CSTR.bit.AAS =1;

I2caRegs.I2CMDR.bit.IRS = 1; // Take I2C out of reset

读取底层驱动如下:

Uint16 uwWriteOrder;

static Uint16 uwWaitCnt = 0;

static Uint16 uwWaitCnt1 = 0;

static Uint16 uwWaitCnt2 = 0;

static Uint16 uwWaitCnt3 = 0;

static Uint16 uwWaitCnt4 = 0;

if(I2caRegs.I2CMDR.bit.STP == 1)

{

DEVICE_DELAY_US(80);

if(++uwWaitCnt1 > 250)

{

uwWaitCnt1 = 250;

return(2);

}

else return(0);

}

else

{

uwWaitCnt1 = 0;

}

uwWriteOrder = 0x50;

I2caRegs.I2CSAR.bit.SAR = uwWriteOrder;

if(I2caRegs.I2CSTR.bit.BB == 1) // Check if bus busy

{

DEVICE_DELAY_US(80);

if(++uwWaitCnt2 > 250)

{

uwWaitCnt2 = 250;

return(2);

}

else return(0);

}

else

{

uwWaitCnt2 = 0;

}

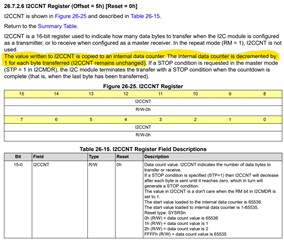

I2caRegs.I2CCNT = 2; // Set data length

I2caRegs.I2CDXR.bit.DATA = (10>>8);

I2caRegs.I2CDXR.bit.DATA = (10&0xff);

I2caRegs.I2CMDR.all = 0x6620;

上面配置完 EEPROM 芯片地址0x50;发送长度,以及相关寄存器后,

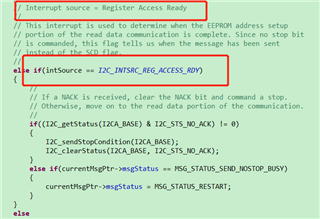

while(I2caRegs.I2CISRC.all != 0x3)

{

DEVICE_DELAY_US(80); //20

if(++uwWaitCnt > 10)

{

uwWaitCnt = 10;

return(2);

}

}

I2caRegs.I2CCNT = 2; // Set data length

I2caRegs.I2CMDR.all = 0x6C20;

系统会一直卡在while(I2caRegs.I2CISRC.all != 0x3) 这里,直到大于delay时间80us,跳出此函数。此时读取SCL和SDA波形,已经发出开始信号,SDA信号在SCL为高时被拉低,紧接着SCL被拉低。但是系统没有将EEPROM芯片的物理地址0x50传送出去。

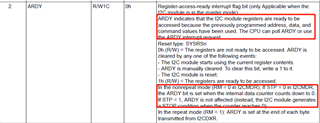

I2caRegs.I2CISRC.all != 0x3 ,Registers ready to be accessed :无法读取IIC寄存器?是因为I2caRegs.I2CIER.ARDY 中断没有触发嘛?

请帮忙分析一下是否有哪里未配置合理,谢谢。