在HVMotorCtrl+PfcKit_v2.0的HVACI_Sensorless_2833x中死区时间的设置有程序

pwm1.Deadband = 2.0*SYSTEM_FREQUENCY; // 120 counts -> 2.0 usec for TBCLK = SYSCLK/1

/* Init Dead-Band Generator for EPWM1-EPWM3*/ \

(*ePWM[ch1]).DBFED = v.Deadband; \

(*ePWM[ch1]).DBRED = v.Deadband; \

(*ePWM[ch2]).DBFED = v.Deadband; \

(*ePWM[ch2]).DBRED = v.Deadband; \

(*ePWM[ch3]).DBFED = v.Deadband; \

(*ePWM[ch3]).DBRED = v.Deadband;

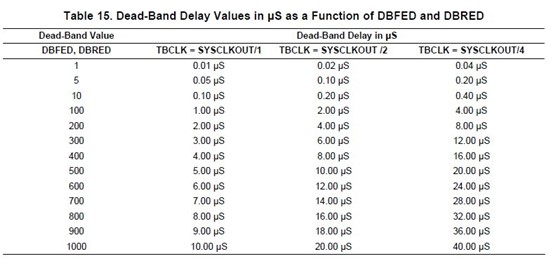

请问算出来的结果pwm1.Deadband即DBFED、DBRED不是应该是300吗?这样的话根据文档TMS320x2833x, 2823x Enhanced Pulse Width Modulator (ePWM) Reference Guide sprug04a里的Dead-Band Delay Values in μS as a Function of DBFED and DBRED不是应该是3μS吗?为什么注释是120 counts 2μS?

还有如果DBFED、DBRED设置的最大值就是1000,不能超过1000?

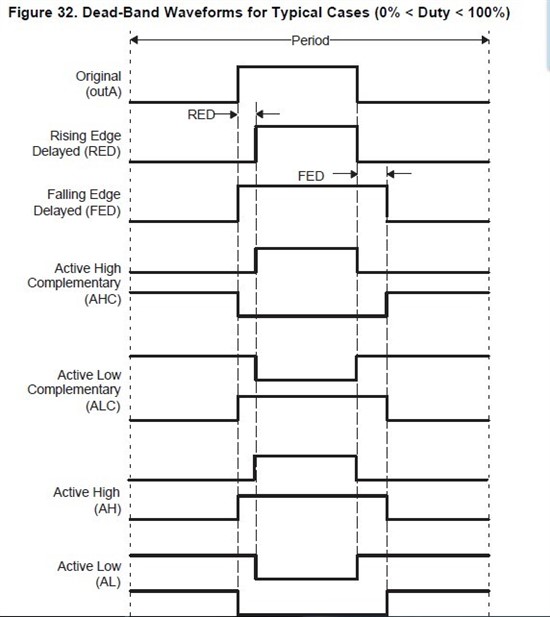

另外根据程序死区的寄存器设置,极性选择为AHC模式,并且Dead-band is fully enabled for both rising-edge delay on output EPWMxA and falling-edge delay on output EPWMxB,DBRED是上升沿延迟,DBFED是下降沿延迟,但是在图中AHC模式中下降沿延迟并没有看到啊,在这个模式中EPWMxB上升沿延迟了,请问这是怎么回事?