Part Number: TMS320F280049

Other Parts Discussed in Thread: C2000WARE

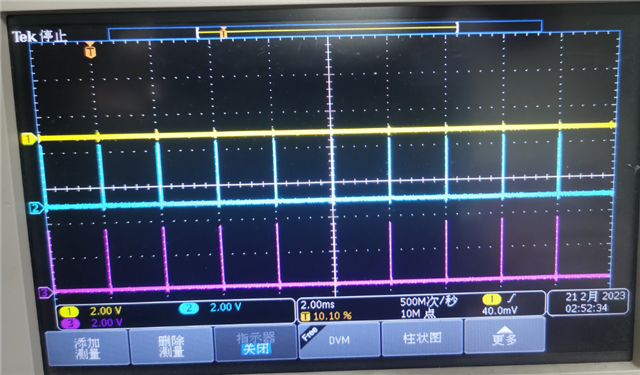

We want that TI DSP to communicate with A3 MCU through SPI interface.However, it was found that the function of enabling pin STE to automatically set high and set low could not be realized through DSP configuration.The DEMO source provided by FAE is also implemented through IO port simulation.As shown in the figures below, SPI read/write enable signal STE is also realized through IO simulation.