hello,

I have a question about the PMBus function.

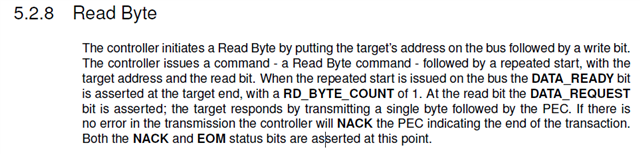

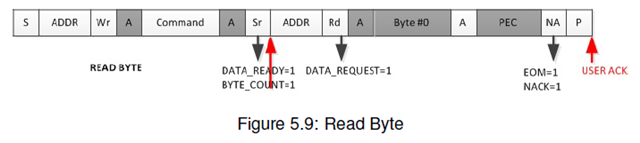

I study the demo code about PMBus design. It only is a test version and there is no more description in datatsheet about the condition that communication is abnormal or not following PMBus protocol.

for example:

0x7E command is a read byte protocol. And we will set send byte count to 1 or (1 + PEC), but if system(master) read 3 or more bytes data.

The state can't be back from PMBUS_STACK_STATE_READ_WAIT_FOR_EOM to PMBUS_STACK_STATE_IDLE.

Beacuse the data of PMBSTS register is 0x241810. No EOM and NACK is received, DATA_REQUEST bit and UNIT_BUSY bit are always set.

Why UNIT_BUSY bit is set and how to clear this bit?