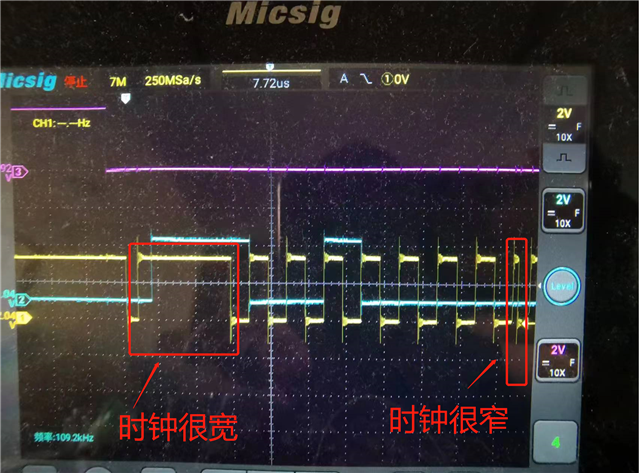

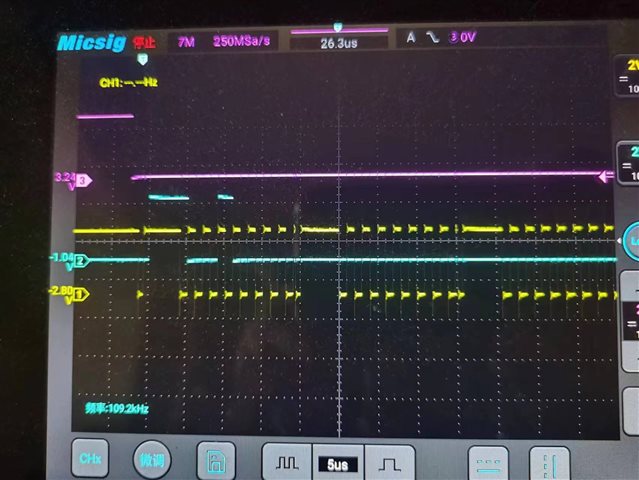

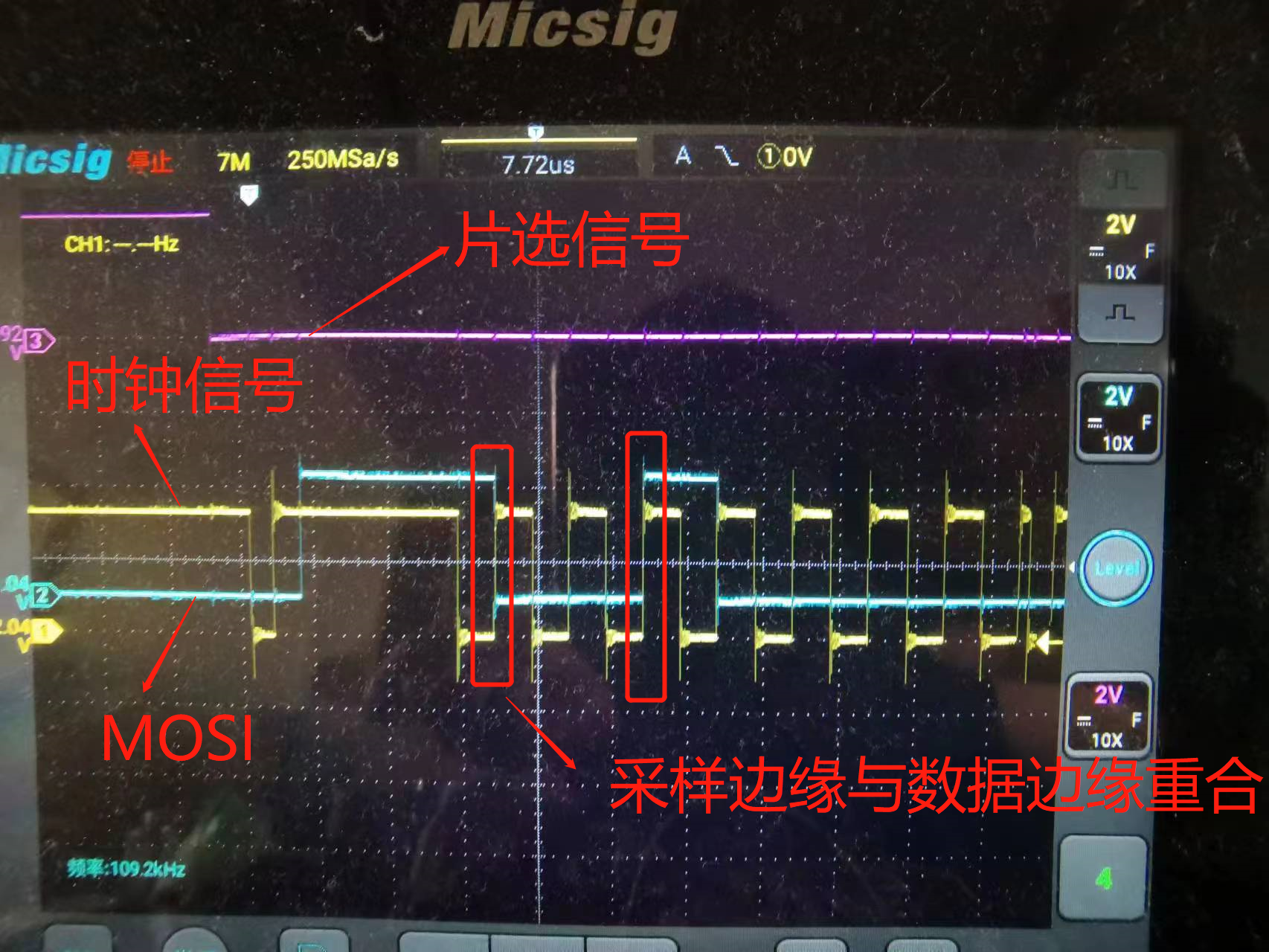

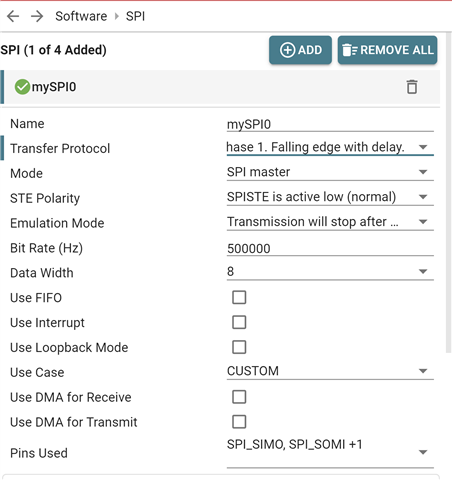

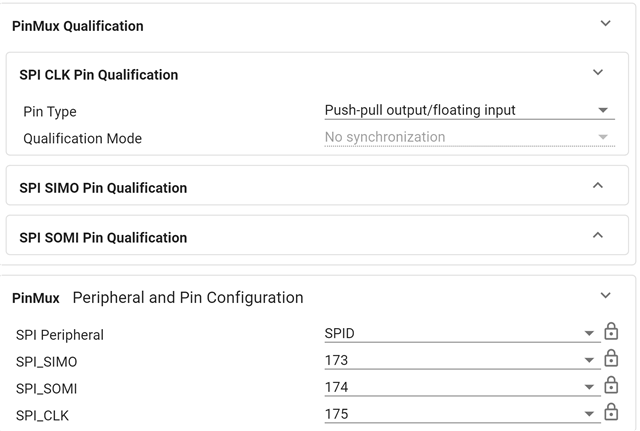

采用syscfg工具配置生成如下SPI初始化代码,访问SPI串行flash,读取器件ID时,向flash发送0x90命令,用示波器测量波形如附图所示,发现DSP芯片产生的波形clock与MOSI线的边缘基本重合,造成无法正确读取器件ID,请问有哪些初始化配置可以优化波形,请指教,谢谢!

void mySPI0_init(){

SPI_disableModule(mySPI0_BASE);

SPI_setConfig(mySPI0_BASE, DEVICE_LSPCLK_FREQ, SPI_PROT_POL1PHA1,

SPI_MODE_MASTER, 500000, 8);

SPI_disableFIFO(mySPI0_BASE);

SPI_disableLoopback(mySPI0_BASE);

SPI_setEmulationMode(mySPI0_BASE, SPI_EMULATION_STOP_AFTER_TRANSMIT);

SPI_enableModule(mySPI0_BASE);

}