Other Parts Discussed in Thread: SYSCONFIG

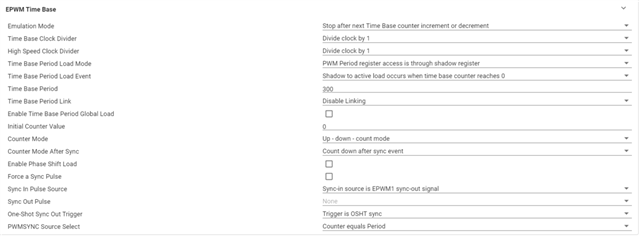

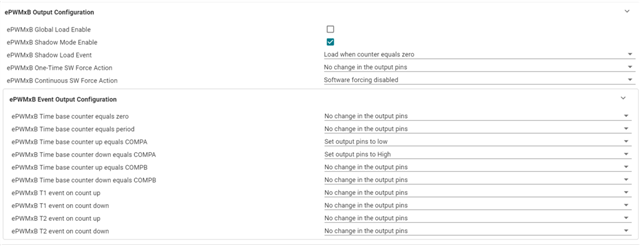

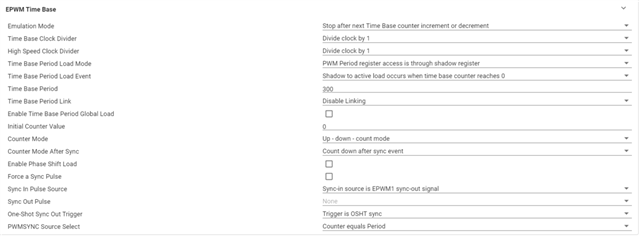

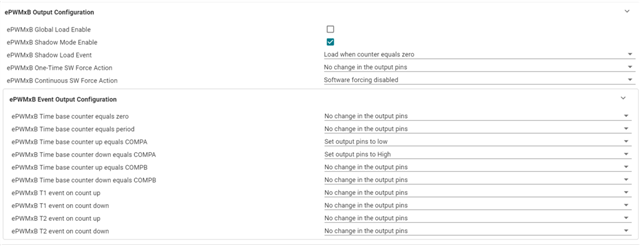

你好,我想請問關於PWM DB的問題,

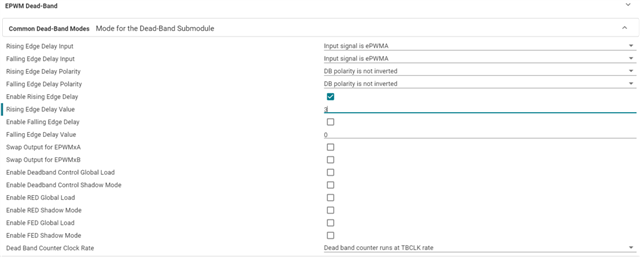

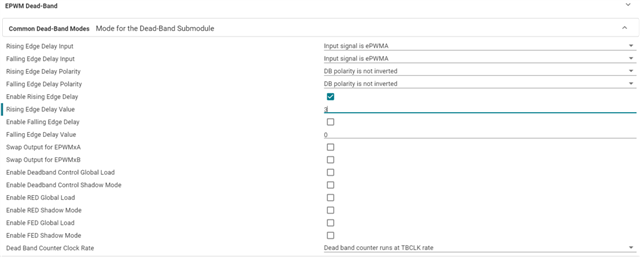

我使用SYSCONFIG設置PWM腳位,想設置PWM1A和PWM1B互補且之間有RED和FED,

目前只有成功輸出互補的PWM,但是沒有RED和FED

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,我想請問關於PWM DB的問題,

我使用SYSCONFIG設置PWM腳位,想設置PWM1A和PWM1B互補且之間有RED和FED,

目前只有成功輸出互補的PWM,但是沒有RED和FED

我的判斷是已經配置成功了。

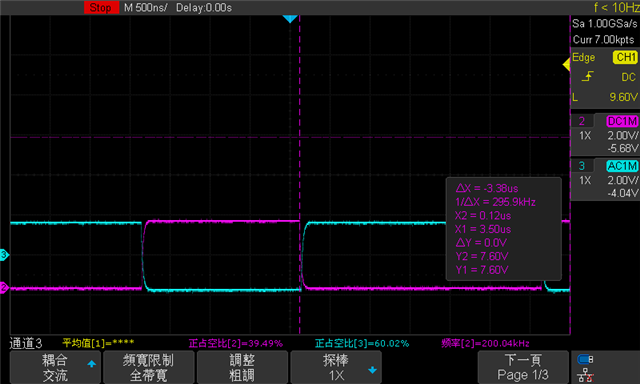

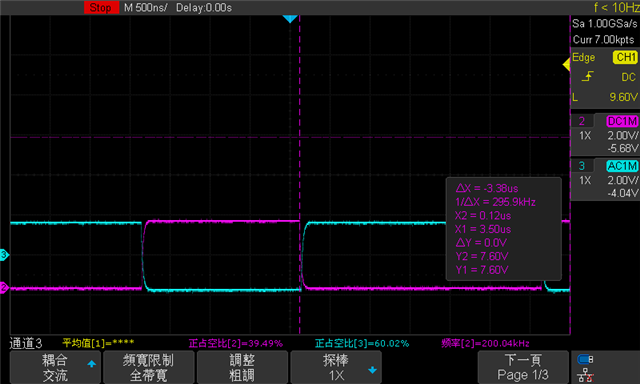

我把Delay Value調高後,有看到明顯的延遲了,謝謝!!

但是當我想同時使用RED和FED時,發現A和B變得不再互補,要將Falling Edge Delay Polarity改成 DB polarity is inverted才又變回互補,是為什麼呢?

我建议你先看一下spruiw9a_TMS320F28003x Real-Time Microcontrollers Technical Reference Manual (Rev. A)第2190页的20.7 Dead-Band Generator (DB) Submodule。

这部分其实并不难理解,主要就是控制各个开关的选择,以及延时的长度。

了解完原理之后,结合syscfg生成的配置代码,会更好的来判断信号的时序。