Part Number: TMS320F280025

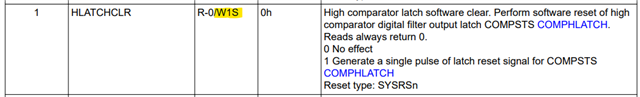

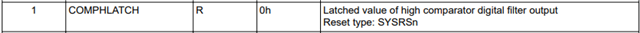

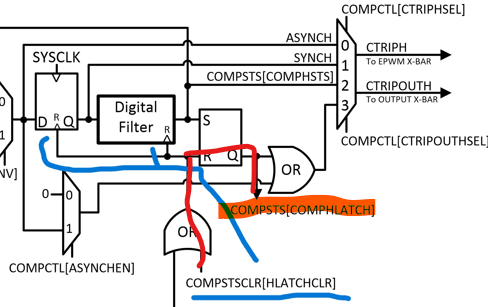

以上图中比较器H为例,如果HLATCHCLR为1,那么经过或门后这个信号会到D触发器的R脚,以及SR触发器的R脚,这会有什么结果?

假设比较器用于过流检测和保护,如果持续发生过流,则ASYNCH、SYNCH和COMPHSTS都为0,还能起到过流保护作用吗?

HLATCHCLR设计的本意应该是用于清除SR触发器的锁存输出,而不应该连接到D触发器的R端,导致同步和异步比较输出信号因为

这个CLR信号被强制处于无效状态(即使真的发生了过流),这是非常危险的。

实际测试也是这样:

H比较器 +端信号 1.20V,DAC输出1400(1.13V),这里顺便说一句,HLATCHCLR似乎不起作用,写1会被自动清零,所以用了HSYNCCLREN位,效果是相同的。

正常OR门输入为0时,H比较器输出为高电平1(1.20>1.12)。如果把HSYNCCLREN位置1,OR门输出为1,导致D触发器、数字滤波器以及SR触发器的RESET端都是1了,结果是ASYNCH、SYNCH以及

COMPHSTS都变成了0,如果这个1.2V是实时电流信号,这实际上就强制让过流保护处于失效状态。