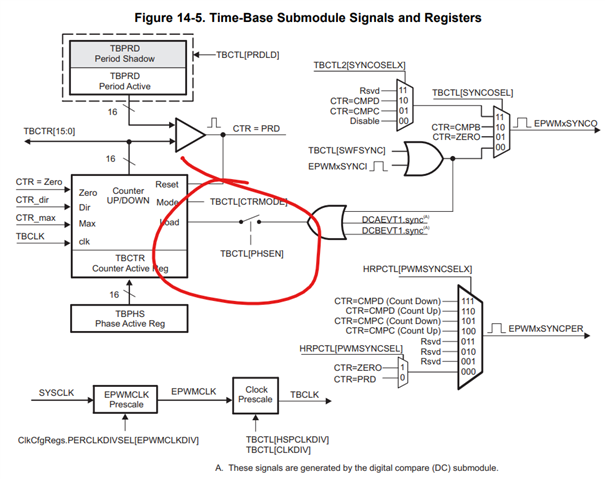

本设计使用了四个EPWM模块(EPWM1\EPWM2\EPWM4\EPWM6),其中EPWM1不使用其输出的PWM波形,只是作为EPWM2\4\6的时基信号,其中EPWM2\4\6配置使用了global load,并利用EPWMXLINK将EPWM4\6都链接到了EPWM2的global load装载上。但实际应用中发现会在几个周期内出现某一次漏装载现象。

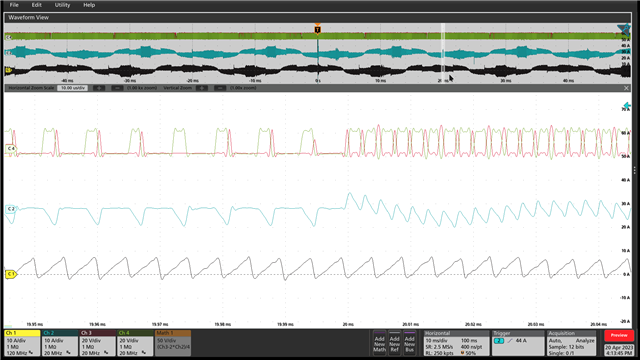

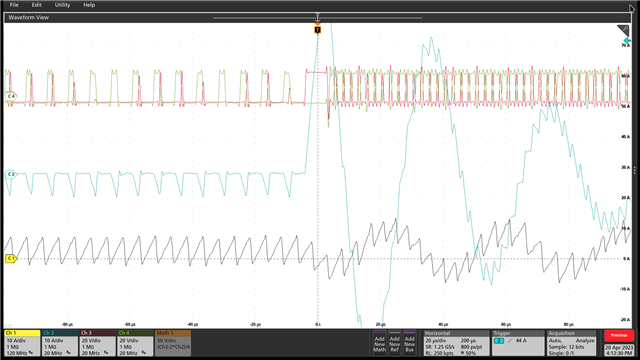

从下图可看到漏装载的是周期值(但我代码里周期值和计数器值都是计算完一起全局装载的),它会在数个50Hz周期内偶然出现一次漏装载现象(计数器装载了,但周期值却没装进去),全局装载并没有很完美的工作

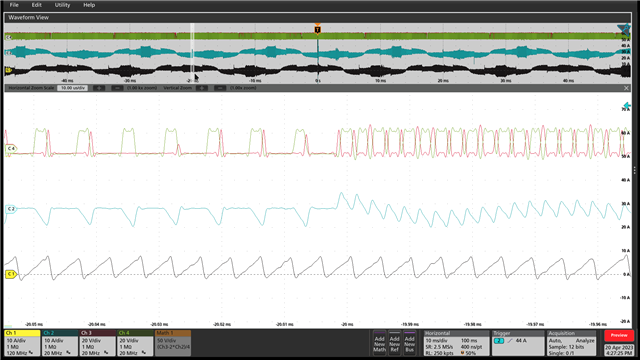

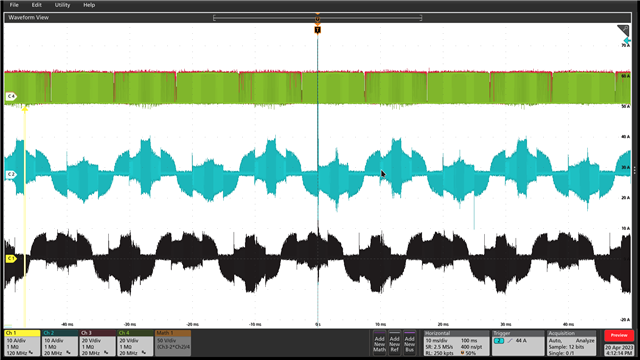

以下两图是其它周期的正常装载现象