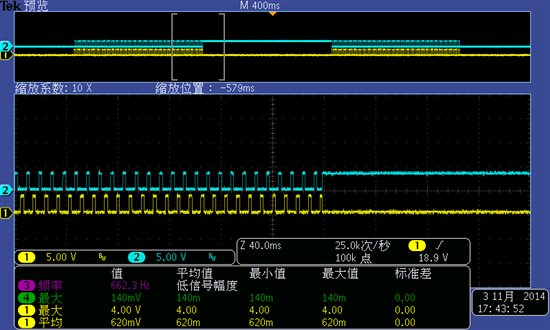

程序开通1s PWM,再关断1s PWM,再开通,再关断,循环进行,在关断前将强制将A、B输入均拉低,偶尔会出现一路(A或B),拉不低情况,代码如下:

//下面为关断PWM

EPwm2Regs.AQSFRC.bit.ACTSFA= 1;

EPwm2Regs.AQSFRC.bit.ACTSFB= 1;

EPwm2Regs.AQSFRC.bit.OTSFA = 1;

EPwm2Regs.AQSFRC.bit.OTSFB= 1;

g_dTBPRD = EPWM2_TIMER_TBPRD;

g_dCMPB = EPWM2_MIN_CMPB;

g_dCMPA = EPWM2_MIN_CMPA ;

EPwm2Regs.TBPRD =g_dTBPRD; //600; // Set timer period 801 TBCLKs

EPwm2Regs.CMPA.half.CMPA = g_dCMPA;//324;//; // Set compare A value

EPwm2Regs.CMPB = g_dCMPB;//276;//;

EALLOW;//关断PWM

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

//下面为开通PWM

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

//图如下