Hi,各位工程师,

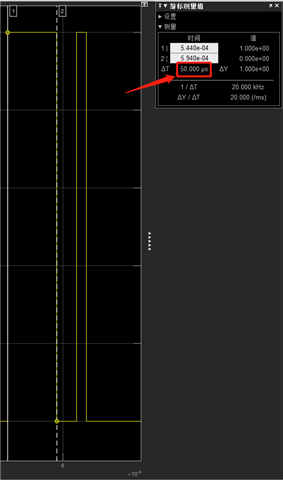

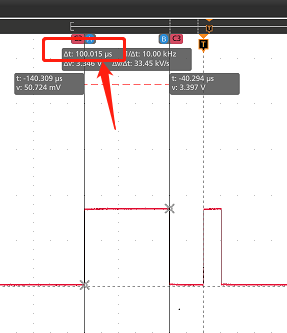

我通过使用简单的逻辑去产生双脉冲信号,如图1,当我将相应的程序烧写到 F2837x controlCARD R1.1 上的 F28377D MCU 后,通过示波器去观察 DSP 输出的双脉冲信号,发现双脉冲信号的宽度(100.015us)为程序中所设计的宽度(50us)的2倍,如图2。

图1 图2

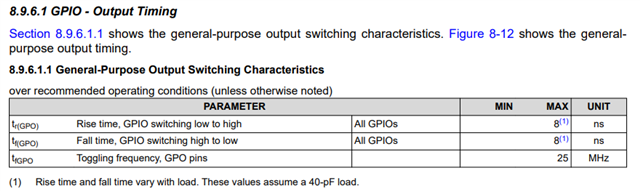

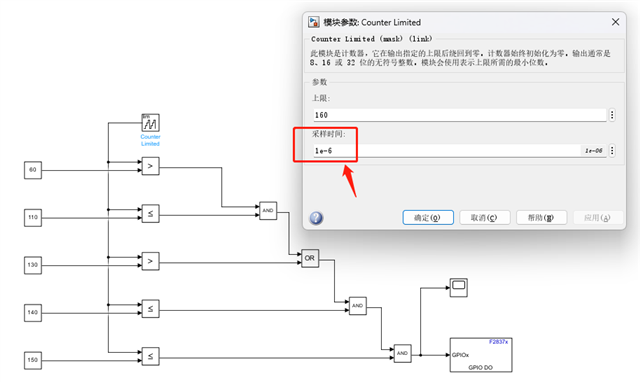

但是,当我在程序中将脉冲信号的宽度增加后,例如由图1的50us增加到500us(通过将图3中的采样时间增加10倍实现),这时通过示波器观察到 DSP 的输出的脉冲信号宽度也为500us。因此我怀疑可能是由于这种纯逻辑或仅采用Timer0的定时中断下切换GPIO的输出的频率限制所引起的问题,或者说是因为图3中采样时间太小引起的问题,这也是整个SIMULINK模型的基础采样时间,所以想要请问一下,该时间的下限大概为多少,这对应可能也是GPIO在某些模式下的工作频率上限。附上我实现以上逻辑的SIMULINK仿真模型,如图3.

图3