请求帮助:

您好!

F28377xd 的SPIFIFO使用问题:

1.SPI 总线在FIFO MOD 下,是否可在FIFO缓存器内连续写两个字(16bits),组成32位长字,然后启动发送;如果设定DLY = 0,是否意味作SPISTE线在连续两个字的发送过程中,维持“Low”。

2.如何实现尼?

十分感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请求帮助:

您好!

F28377xd 的SPIFIFO使用问题:

1.SPI 总线在FIFO MOD 下,是否可在FIFO缓存器内连续写两个字(16bits),组成32位长字,然后启动发送;如果设定DLY = 0,是否意味作SPISTE线在连续两个字的发送过程中,维持“Low”。

2.如何实现尼?

十分感谢!

你好,

.SPI 总线在FIFO MOD 下,是否可在FIFO缓存器内连续写两个字(16bits),组成32位长字,然后启动发送;

参考下图,应该是可以的。

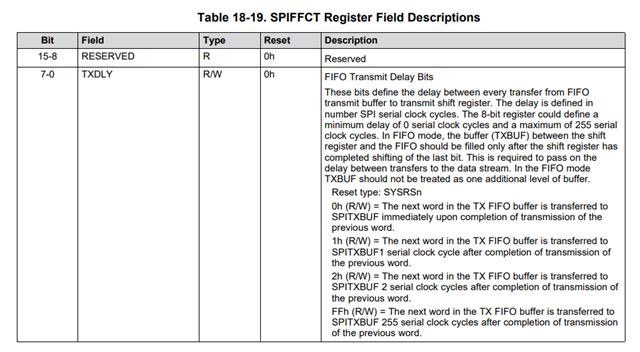

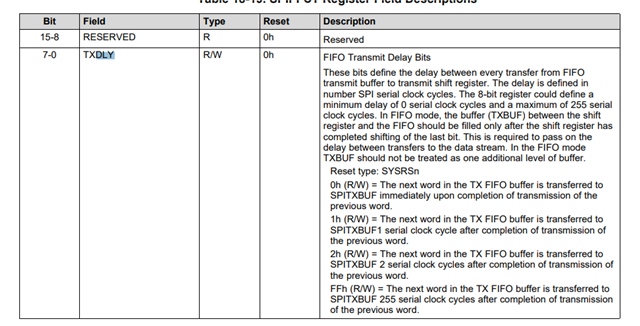

如果设定DLY = 0,是否意味作SPISTE线在连续两个字的发送过程中,维持“Low”。

你是指这个位吗? 这跟SPISTE没有关系吧?

是的,如果您将两个 16 位字符连续写入 FIFO,SPI 将使用一个 SPISTE 脉冲来传输它们。