1. 软件版本

C2000Ware 版本:C2000Ware_5_00_00_00

Code Composer Studio 版本: Version: 12.4.0.00007

验证设备:ControlCard - TMDSCNCD28388D

2. 问题1描述

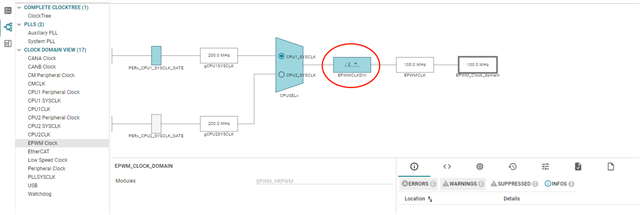

使用 CCS 导入 C2000Ware 中的 Universal project 时,Syscfg 工具可以配置系统时钟树。默认 EPWM 的分频系数如下:

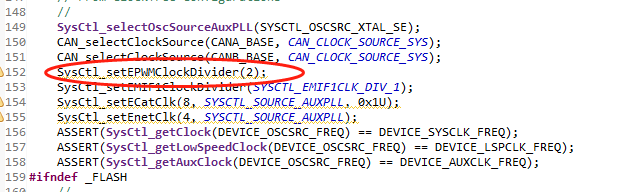

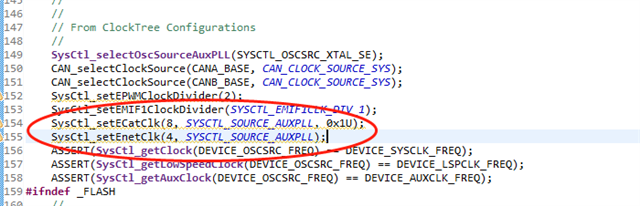

然而,当打开该工程生成的 device.c 文件时,Syscfg 似乎生成了不正确的分频系数配置,如下图:

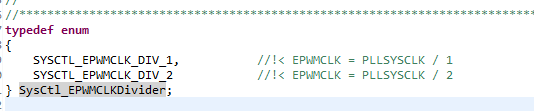

SysCtl_setEPWMClockDivider 函数的参数默认结构如下:

如果此时传入参数为 2,已经超出了枚举定义的范围。如果取最低一位的话,那么此时的分频系数为 SYSCTL_EPWMCLK_DIV_1 ,使得最终设置的 EPWMCLK 为 200Mhz,与所期望的不符。此外,如果修改 EPWM 的分频系数为 1 ,那么此时 Syscfg 生成 SysCtl_setEPWMClockDivider 函数后传入参数为 1 , 相当于 SYSCTL_EPWMCLK_DIV_2 ,使得设置的 EPWMCLK 为 100Mhz,同样与所期望的不符。

通过示波器验证后发现问题确实存在。同时,类似的问题似乎也存在于 EtherCAT 的时钟配置函数 SysCtl_setECatClk 和 Ethernet 的时钟配置函数 SysCtl_setEnetClk 。

3. 问题2描述

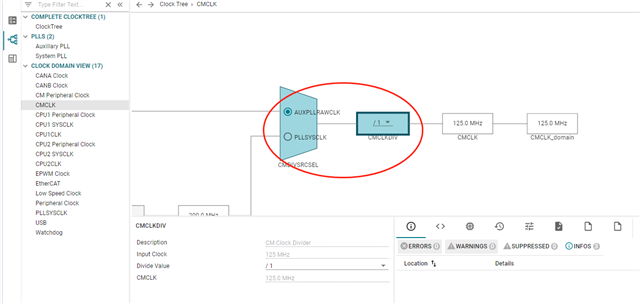

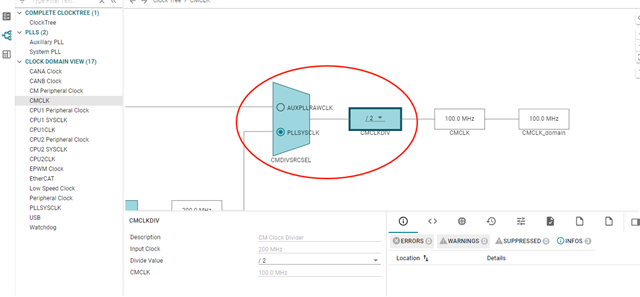

同样使用 CCS 导入 C2000Ware 中的 Universal project 并尝试配置 CMCLK 时,如果修改其时钟源和分频系数,似乎不会反应在生成的代码中。修改前后如下:

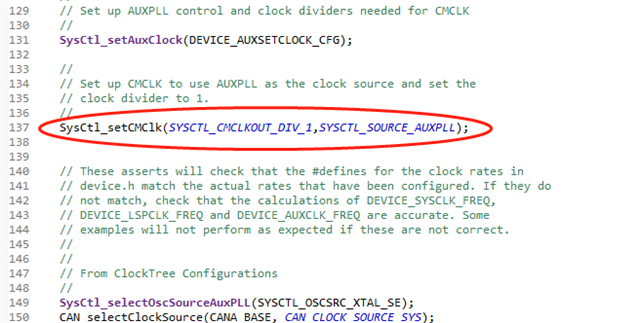

修改前后生成的 device.c 文件中关于 CMCLK 的配置部分似乎保持不变,如下:

猜测该部分并未完全归 Clock tree 管理,但是在界面中却显示支持。

4. 问题解决建议

针对问题1,Syscfg 生成函数时传参尽量使用宏定义而不是具体的值;针对问题2,可能需要手动将生成的内容修改。