Part Number: TMS320F280025

Other Parts Discussed in Thread: C2000WARE

例程路径D:\ti\c2000\C2000Ware_4_00_00_00\driverlib\f28002x\examples\i2c\CCS

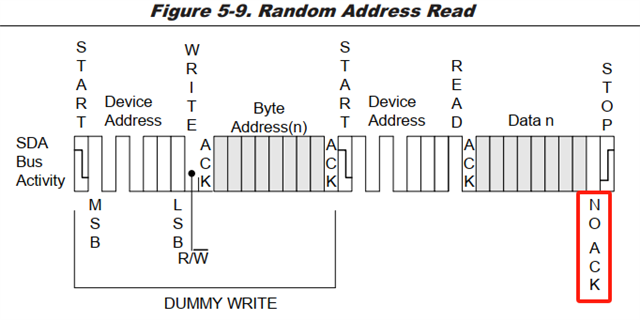

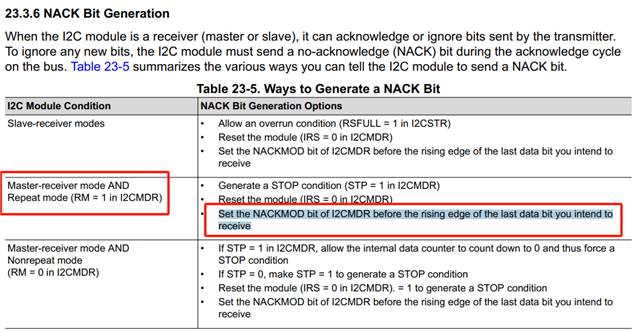

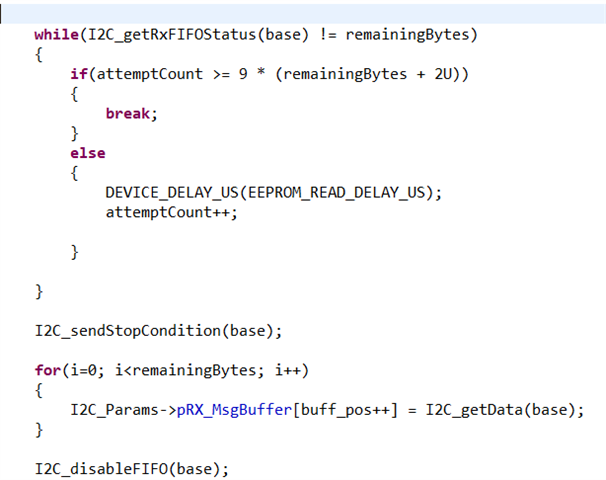

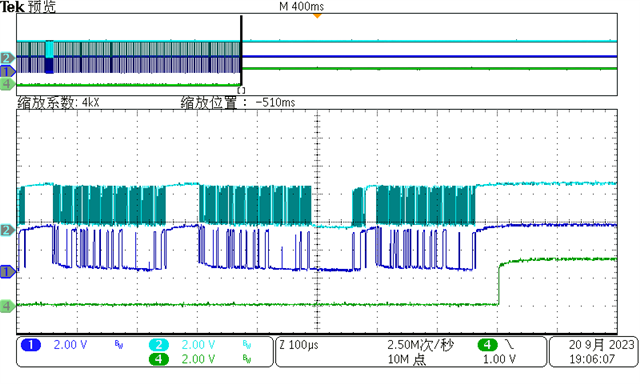

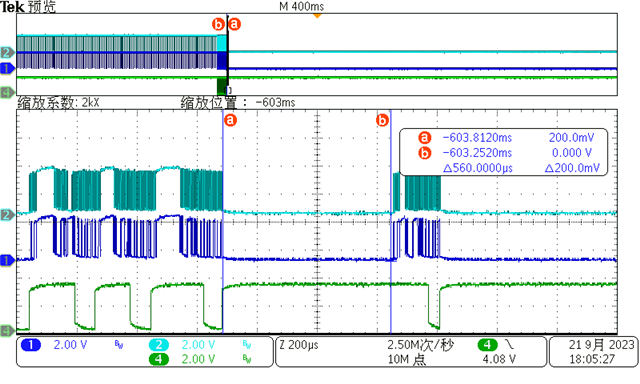

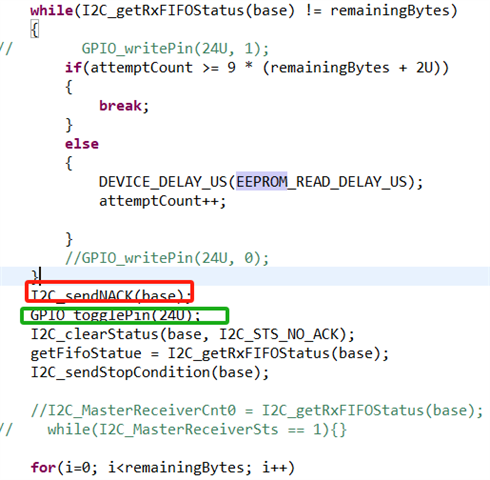

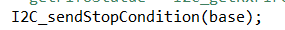

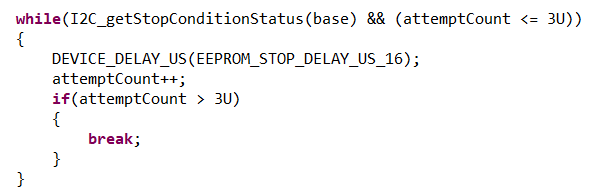

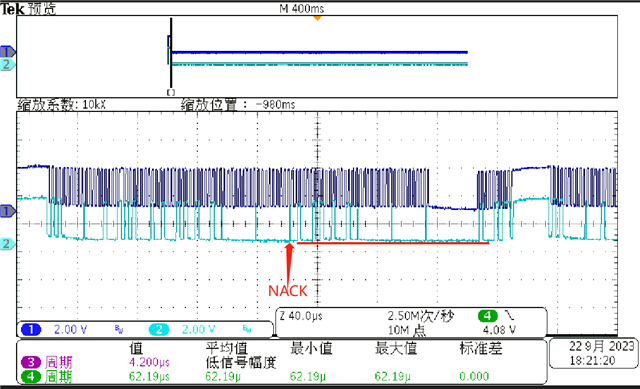

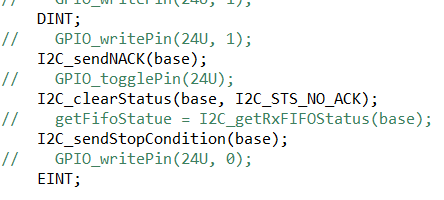

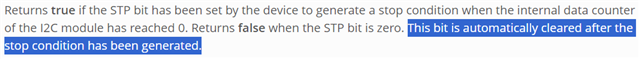

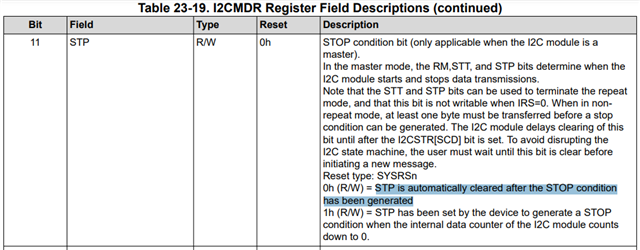

我是用的是polling方式对E2PROM进行读写,在E2prom芯片手册中,随机读取时序最后是要求主机发送一个NACK位,但是例程中却没有发送。我查看芯片技术手册,如下图所示,需要在最后一个bit的上升沿发送NACK,请问在FIFO中如何操作呢,如何在FIFO模式下,正确发送NACK位呢