Other Parts Discussed in Thread: C2000WARE

在官方的例程 project i2c_ex6_eeprom_interrupt from C:\ti\c2000\C2000Ware_4_03_00_00\driverlib\f2837xs\examples\cpu1\i2c.中

有下面一段发送数据的代码

145行:将待写入的目标地址写入Temp

147行:取出了temp的低24位数据,这里为啥是取低24位呢,是因为目标寄存器的存储区间最大只能到2^24吗?

149行:把待传输数据的字节数左移了24位,并与之前的temp进行了与操作。因此得到的temp,高8位,表示待传输的字节个数,低24位,表示待传输的目标地址

154行:因为待传输的目标地址字节数为2,因此for循环里的i,其实就是从1减到0,只有两个循环操作。这样的话,156行,就仅仅将temp的8~16位(对应i=1)和0~7位(对应i=0)写入了FIFO发送寄存器

那temp的其位数也并没有进行传输使用到吗?这里知识把目标地址寄存器的低16位数据发送了出去吗?

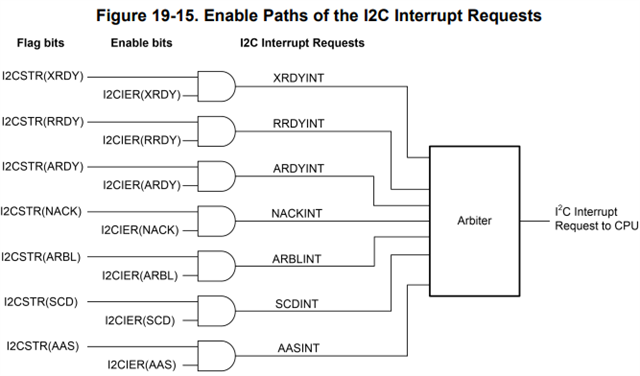

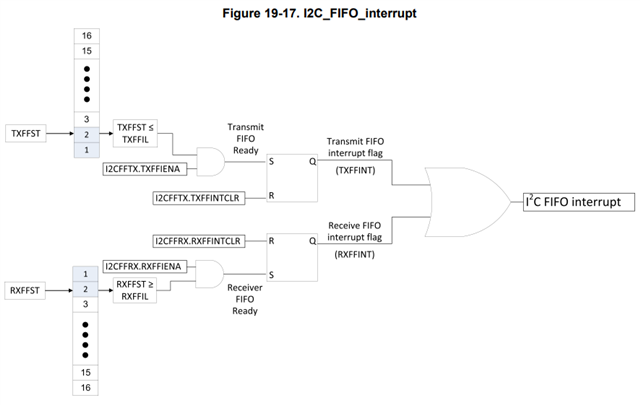

另外,还想再补充咨询下,这里因为把FIFO的发送寄存器深度设置为0,因此把这两个字节的数据发送出去后,就会进入FIFO中断吗?但141行也设置了寄存器发送个数为2,那这样2个字节发送完毕后也会产生NACK和STOP信号吧?为啥不会触发这两个对应的中断呢?软件里相应的中断也被使能了

这里设置了发送数据个数为2,但在随后又修改了发送数据个数,为(地址字节个数+待发送数据字节个数)。但是到了这一步的时候,,地址字节不是已经通过I2C_TransmitSlaveAddress_ControlBytes()函数发送出去了吗