最近在研究三相交错LLC的开环驱动,手动控制频率变化后会有一路驱动常高或者常低的现象。

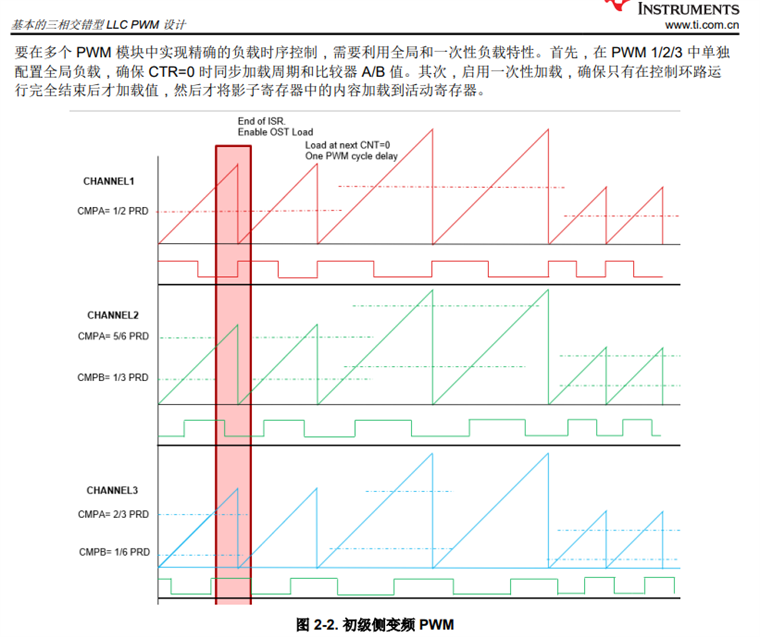

ti有一份官方文档也是说明多相控制的问题《利用新型 ePWM 特性进行多相控制》,链接为:www.ti.com.cn/.../zhcaax8.pdf

看完后针对测试出现的情况进行了分析,但仍有些疑问,希望可以得到TI工程师的确认。

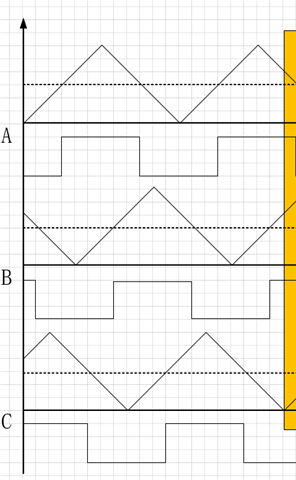

前提:ABC三相分别对应EPWM1/2/3,其中2和3都link到1,2滞后1 120°,3超前1 120°,pwm计数方式都为增减计数,

中断中更新PRD和TBPHS(TBPHS = 2/3*PRD),2接收到同步信号后接收相移值并变为减计数,3为增计数。

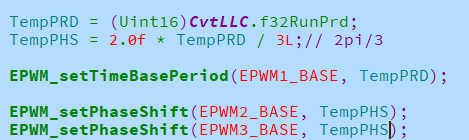

基本驱动时序逻辑和中断改变代码如下:

第一个问题:

虽然PWM2和PWM3link到PWM1,这里有一个疑问,当改变PWM1的PRD值时,是不是PWM1/2/3的PRD 影子寄存器的值

被更新,而相应的活动寄存器要等各自的计数器过零才会加载影子寄存器的值,而这三个时基各差120°,那么PRD更新实际上

是不是也差了120度(这是我的猜测不确定)。

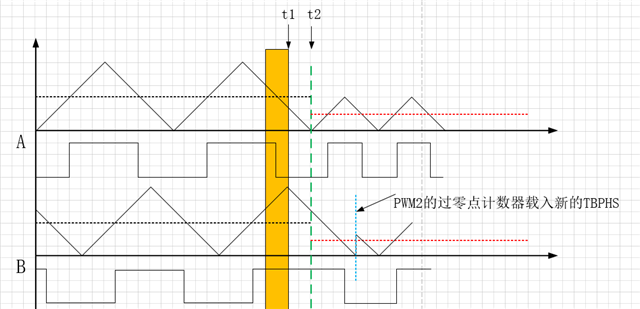

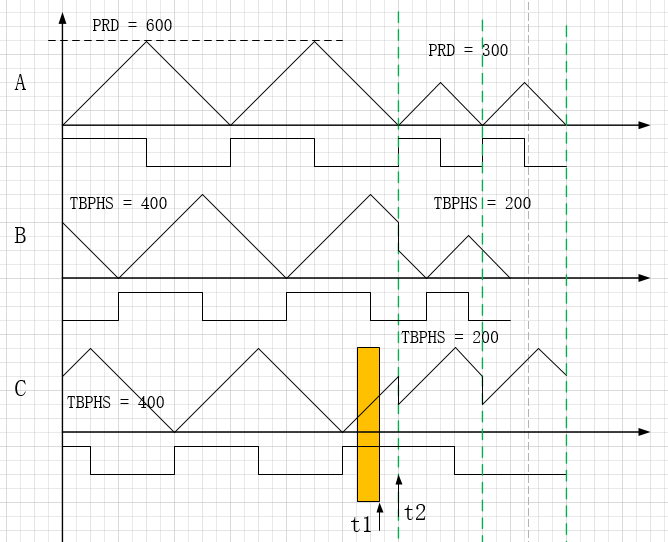

然后来看下面的时序图,PRD从大变为小时,黄色代表中断运行结束,即PRD已经写入影子寄存器,TBPHS直接更新:

t1时刻,中断运行结束,即PRD已经写入各个影子寄存器,TBPHS是直接更新:

t2时刻,PWM1计数过零,产生同步信号,同时PWM1的PRD活动寄存器被更新(2和3未更新,因为2和3自己的计数器未过零),对2和3,计数器加载TBPHS值,2配置为加载后向下计数,3为向上计数。

2的计数器过零后,2的PRD更新,计数器更新为TBPHS,减计数,在下一个同步信号过来前已降为0。

但对3,由于是向上计数,且PRD未更新,为旧PRD值,到减计数时还未到0,新的PWM1同步信号到来,然后计数器反向,,后续永远无法过零,故维持之前的低电平(若取值合适似乎也能使其一直维持高电平)。

实际测试异常波形如下:

对第一个问题,我的分析是否正确?

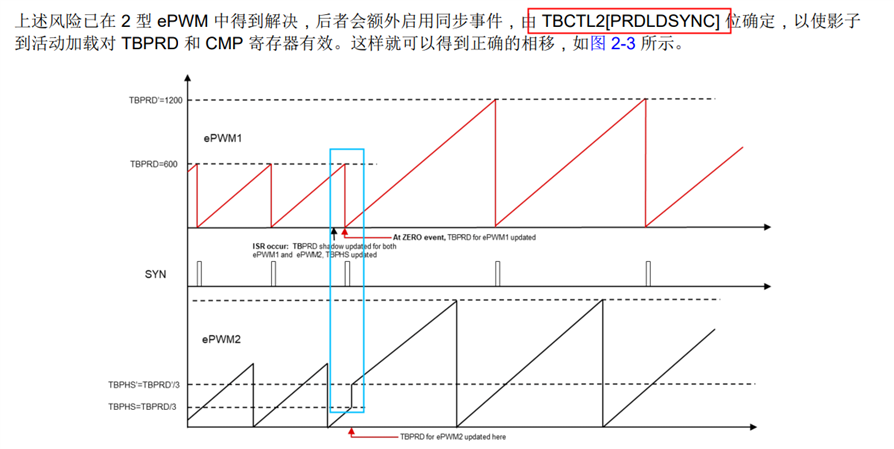

如果正确的话,上面的那份官方文档确实也给出了解决方案,即在同步信号到来时同步加载PRD值。这样对上面描述的情况不需要等到PWM的过零点才加载PRD值。(暂时还未验证)

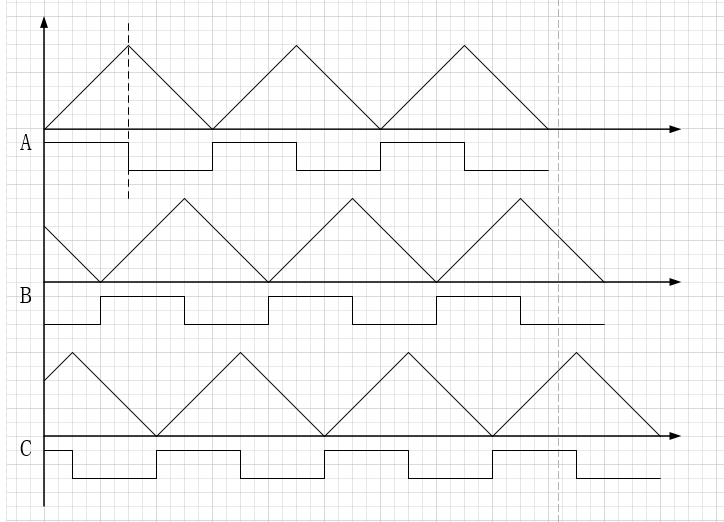

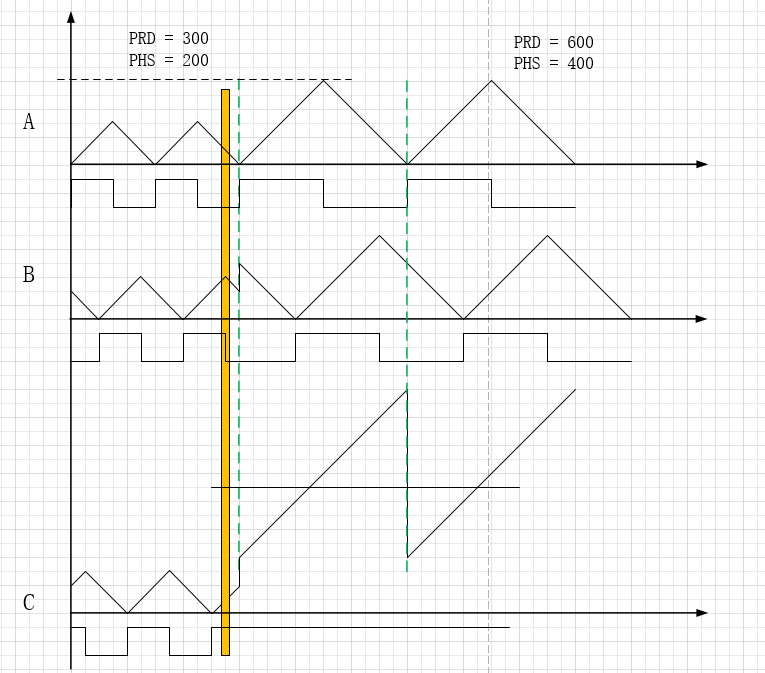

第二个问题,PRD从小变为大时,也会出现PWM3驱动丢失的情况,如下:

且我还想确认一个问题,就是TBPHS比PRD大时,输出高低电平都有可能,会保持同步信号到来前的电平?

实际测试是高低电平都有可能。

这种情况我的分析是:原来PRD为300,PHS为200;更新后PRD为600,PHS为400,

同步信号到来时3的计数值更新为400,比旧PRD值大,所以计数器一直增直到下一次同步信号到来。

(这里似乎直接用第一个问题的解决方法就可以解决,我写到后面才发现)

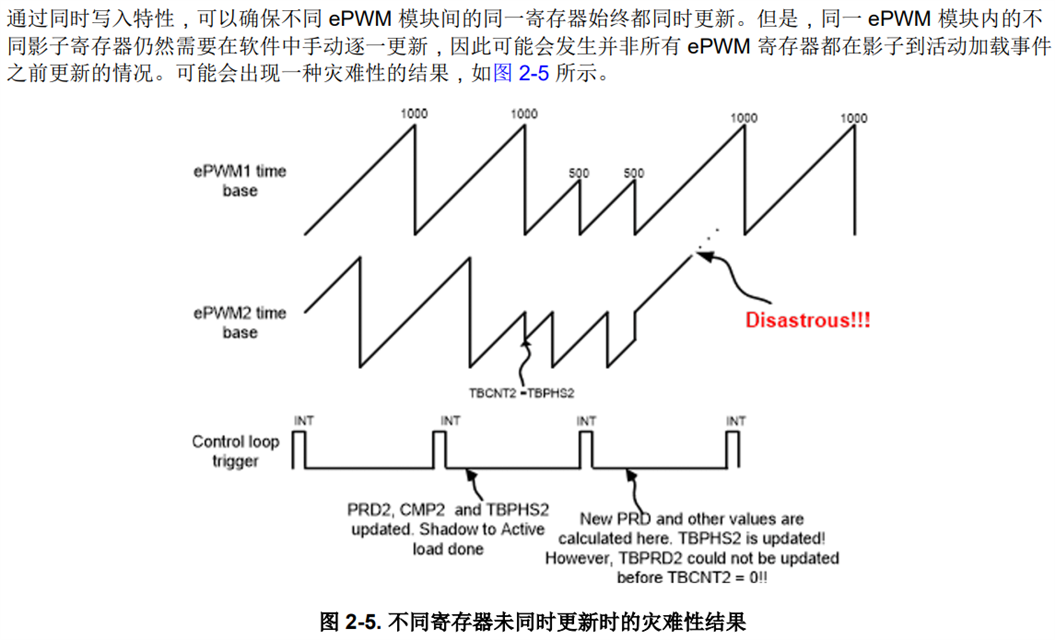

这个问题和文档中描述的异常是相似的

针对这个问题,文档中提到了全局加载和一次性加载的配置。

我看了相关描述,不知道理解的是否到位:

全局加载是针对单个PWM模块的,比如PWM1的PRD,CMPA,CMPB都有更新,但是代码为三句,配置需要时间,假设配置刚好跨越计数器过零点,那么会导致时序紊乱。

一次性加载似乎就是用来链接几个pwm模块间的全局加载

这里我又有疑问:如果链接了2和3的GLDCTL2到1。那么按照我上面的三相驱动逻辑,假设在PWM1的计数器 过零点前 中断运行结束,并触发一次性加载,那么随之到来的CTR=0,触发1的全局加载,

同时2和3的全局加载也会触发么? 如果是的话,这样上面第2个问题似乎就解决了。(感觉也应该是这样,不然好像一次性加载没意义)

如果不是是在2和3的CTR过零点触发全局加载么?

问题有点多,也是这两天测试碰到的所有问题,希望可以得到TI工程师的解答。