Part Number: TMS320F280039

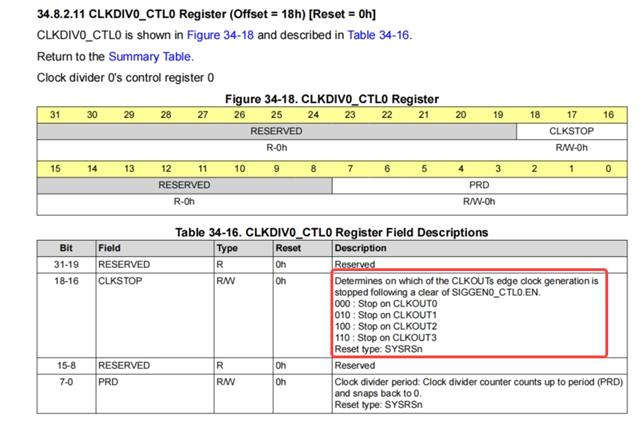

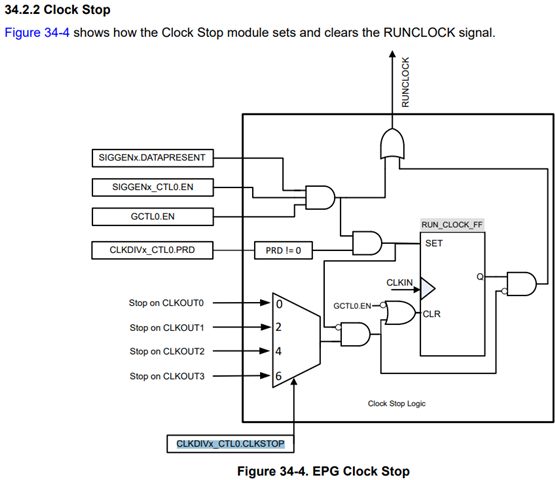

CLKSTOP 当SIGGEN0_CTL0清零时,时钟生成可以选择CLKOU0-CLKOUT3的下降沿检测停止;

目前我配置如下:

时钟分频周期clk_prd=32;clkdiv0_dclk[0]的时钟偏移量配置为0,clkdiv0_dclk[1]的时钟偏移量配置为0x10,CLKSTOP选择CLK0或者CLK1下降沿停止时,将CLK0_DCLK 和 CLK1_DCLK 输出到GPIO口

当修改CLKSTOP=0X0, 我认为clk0关闭后 clk1 就应当关闭了,当修改CLKSTOP=0X2, 我认为clk1关闭后 clk0 就应当关闭了,实际二者测量结果无区别;

如何理解这个bit位呢?