TI工程师,你好

例子:默认为100kHz

#define PWM_PRD (60000/200) // Period count = 300 corresponding to 100 KHz @ 60 MHz (Up-Down count mode)

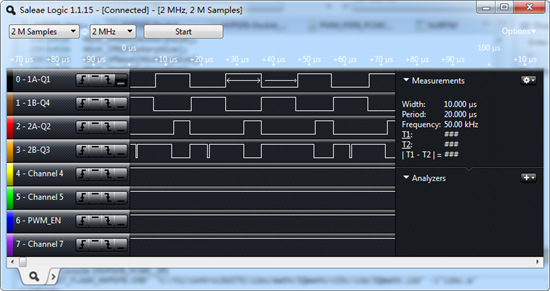

我这边需要修改为40kHz

#define PWM_PRD (60000/80) // Period count = 300 corresponding to 100 KHz @ 60 MHz (Up-Down count mode)

除了改这个地方,还需要修改哪些代码?