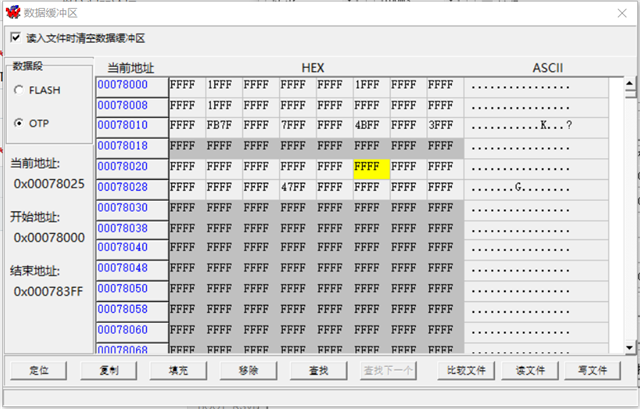

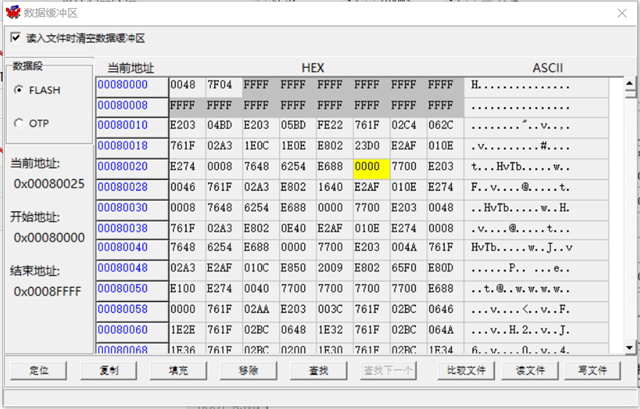

1、f28002x_dcsm_z1otp.asm中已经配置的加密;

2、280025_FLASH_lnk.cmd配置了DCSM的地址;

3、f28002x_headers_nonbios.cmd中注释// DCSMBANK0Z1OTP : origin = 0x00078000, length = 0x00000020, 已通过编译

4、

实际OTP和FLASH区域数据并未被加密

实际OTP和FLASH区域数据并未被加密

;;#############################################################################

;;

;; FILE: f28002x_dcsm_z1otp.asm

;;

;; TITLE: Dual Code Security Module Zone 1 OTP

;;

;; DESCRIPTION:

;;

;; This file is used to specify Z1 DCSM OTP and zone select block

;; values to program.

;;

;; In addition, the 60 reserved values after the zone select block

;; are all programmed to 0x0000 as well.

;;

;; !!IMPORTANT!! The below memory sections are mapped to OTP (one-time

;; programmable) memory with the *dcsm_lnk.cmd linker command file. In order

;; to program the below memory sections, user should uncomment the .long words

;; of each section and change the value to what is desired. Additionally, the

;; corresponding section of *dcsm_lnk.cmd should no longer be labelled as a

;; dummy section. Remove ", type = DSECT" in SECTIONS from the memory section

;; that is being programmed.

;;

;;

;; !!IMPORTANT!! The "bx_dcsm_otp_z1_linkpointer" section contains the

;; Z1 LINKPOINTER which determines the location of the Z1 Zone Select block.

;; If the LINKPOINTER is changed, then the "bx_dcsm_zsel_z1_linkpointer"

;; section in the *_dcsm_lnk.cmd command linker file must also change to an

;; address decoded from the value specified in the Z1-LINKPOINTER location.

;;

;; The "bx_dcsm_zsel_z1" section contains the actual Z1 Zone Select Block

;; values that will be linked and programmed into to the DCSM Z1 OTP Zone

;; Select block in OTP.

;; These values must be known in order to unlock the CSM module.

;; Refer TRM for default values for the password locations.

;;

;; It is recommended that all values be left as at default during code

;; development. When code development is complete, modify values as required.

;; The new values has to take ECC values as well in to consideration (only bits

;; with value of '1' can be changed to '0' and NOT vice versa).

;;

;; TI ships this example commenting out the initialization of all the

;; below locations, users need to enable them for programming these values.

;;

;;#############################################################################

;; $TI Release: F28002x Support Library v3.04.00.00 $

;; $Release Date: Fri Feb 12 18:58:34 IST 2021 $

;; $Copyright:

;// Copyright (C) 2021 Texas Instruments Incorporated - http://www.ti.com/

;//

;// Redistribution and use in source and binary forms, with or without

;// modification, are permitted provided that the following conditions

;// are met:

;//

;// Redistributions of source code must retain the above copyright

;// notice, this list of conditions and the following disclaimer.

;//

;// Redistributions in binary form must reproduce the above copyright

;// notice, this list of conditions and the following disclaimer in the

;// documentation and/or other materials provided with the

;// distribution.

;//

;// Neither the name of Texas Instruments Incorporated nor the names of

;// its contributors may be used to endorse or promote products derived

;// from this software without specific prior written permission.

;//

;// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

;// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

;// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

;// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

;// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

;// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

;// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

;// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

;// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

;// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

;// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

;// $

;;#############################################################################

.sect "b0_dcsm_otp_z1_linkpointer"

.retain

.long 0x1FFFFFFF ;Z1-LINKPOINTER1

.long 0xFFFFFFFF ;Reserved

.long 0x1FFFFFFF ;B0_Z1OTP_LINKPOINTER2

.long 0xFFFFFFFF ;Reserved

.long 0x1FFFFFFF ;B0_Z1OTP_LINKPOINTER3

.long 0xFFFFFFFF ;Reserved

.sect "b0_dcsm_otp_z1_gpreg"

.retain

;; See the ROM Code and Peripheral Booting chapter of TRM for more details.

;;

;; Below is a description of the bit fields of Z1OTP_BOOTPIN_CONFIG

;; used by Boot ROM.

;;

;; | Key (31-24) | BMSP2 (23-16) | BMSP1 (15-8) | BMSP0 (7-0) |

;;

;; Below is a description of the bit fields of Z1OTP_GPREG2 used by

;; Boot ROM.

;;

;; | Key (31-24) | RSVD (23-8) | RSVD (7-6) | ESP (5-4) | RSVD (3-0) |

;;

.long 0xFFFFFFFF ;Z1OTP_BOOTPIN_CONFIG

.long 0xFFFFFFFF ;Z1OTP_GPREG2

.sect "b0_dcsm_otp_z1_pswdlock"

.retain

.long 0xFB7FFFFF ;Z1-PSWDLOCK

.long 0x7FFFFFFF ;Reserved

.sect "b0_dcsm_otp_z1_crclock"

.retain

.long 0x4BFFFFFF ;Z1-CRCLOCK

.long 0x3FFFFFFF ;Reserved

.sect "b0_dcsm_otp_z1_bootctrl"

.retain

;; See the ROM Code and Peripheral Booting chapter of TRM for more details.

;;

;; Below is a description of the bit fields of Z1OTP_BOOTDEF_LOW used by

;; Boot ROM.

;;

;; | BOOT_DEF3(31-24) | BOOT_DEF2(23-16) | BOOT_DEF1(15-8) | BOOT_DEF0(7-0) |

;;

;; Below is a description of the bit fields of Z1OTP_BOOTDEF_HIGH

;; used by Boot ROM.

;;

;; | BOOT_DEF7(31-24) | BOOT_DEF6(23-16) | BOOT_DEF5(15-8) | BOOT_DEF4(7-0) |

;;

;; .long 0xFFFFFFFF ;Z1OTP_BOOTDEF_LOW

;; .long 0xFFFFFFFF ;Z1OTP_BOOTDEF_HIGH

.sect "b0_dcsm_zsel_z1"

.retain

.long 0xFFFFFFFF ;Z1-EXEONLYRAM

.long 0xFFFFFFFF ;Z1-EXEONLYSECT

.long 0xFFFFFFFF ;Z1-GRABRAM

.long 0xFFFFFFFF ;Z1-GRABSECT

.long 0xFFFFFFFF ;Z1-CSMPSWD0 (LSW of 128-bit password)

.long 0x47FFFFFF ;Z1-CSMPSWD1 // this value is for ZSB0

.long 0xFFFFFFFF ;Z1-CSMPSWD2

.long 0xFFFFFFFF ;Z1-CSMPSWD3 (MSW of 128-bit password)

.sect "b1_dcsm_otp_z1_linkpointer"

.retain

;; .long 0x1FFFFFFF ;B1_Z1OTP_LINKPOINTER1

;; .long 0xFFFFFFFF ;Reserved

;; .long 0x1FFFFFFF ;B1_Z1OTP_LINKPOINTER2

;; .long 0xFFFFFFFF ;Reserved

;; .long 0x1FFFFFFF ;B1_Z1OTP_LINKPOINTER3

;; .long 0xFFFFFFFF ;Reserved

.sect "b1_dcsm_zsel_z1"

.retain

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;B1_Z1OTP_EXEONLYSECT

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;B1_Z1OTP_GRABSECT

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;Reserved

;;----------------------------------------------------------------------

;; For code security operation,after development has completed, prior to

;; production, all other zone select block locations should be programmed

;; to 0x0000 for maximum security.

;; If the first zone select block at offset 0x10 is used, the section

;; "dcsm_rsvd_z1" can be used to program these locations to 0x0000.

;; This code is commented out for development.

;; .sect "dcsm_rsvd_z1"

;; .retain

;; .loop (1e0h)

;; .int 0x0000

;; .endloop

;;#############################################################################

;; End of file

;;#############################################################################

MEMORY

{

PAGE 0 : /* Program Memory */

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* RAMLS4 : origin = 0x0000A000, length = 0x00000800

RAMLS5 : origin = 0x0000A800, length = 0x00000800

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800 */

/* Combining all the LS RAMs */

// RAMLS4567 : origin = 0x0000A000, length = 0x00002000

RAMLS4567 : origin = 0x0000A000, length = 0x00001800

RAMLS7 : origin = 0x0000b800, length = 0x00000800

RAMGS0 : origin = 0x0000C000, length = 0x000007F8

// RAMGS0_RSVD : origin = 0x0000C7F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* Z1 OTP. LinkPointers */

DCSM_OTP_Z1_LINKPOINTER : origin = 0x78000, length = 0x00000C

/* Z1 OTP. GPREG1/GPREG2 */

DCSM_OTP_Z1_GPREG : origin = 0x7800C, length = 0x000004

/* Z1 OTP. PSWDLOCK/RESERVED */

DCSM_OTP_Z1_PSWDLOCK : origin = 0x78010, length = 0x000004

/* Z1 OTP. CRCLOCK/RESERVED */

DCSM_OTP_Z1_CRCLOCK : origin = 0x78014, length = 0x000004

/* Z1 OTP. RESERVED/BOOTCTRL */

DCSM_OTP_Z1_BOOTCTRL : origin = 0x7801C, length = 0x000004

/* DCSM Z1 Zone Select Contents (!!Movable!!) */

/* Z1 OTP. Z1 password locations / Flash and RAM partitioning */

DCSM_ZSEL_Z1_P0 : origin = 0x78020, length = 0x000010

/* Z2 OTP. LinkPointers */

// DCSM_OTP_Z2_LINKPOINTER : origin = 0x78200, length = 0x00000C

/* Z2 OTP. GPREG1/GPREG2 */

// DCSM_OTP_Z2_GPREG : origin = 0x7820C, length = 0x000004

/* Z2 OTP. PSWDLOCK/RESERVED */

// DCSM_OTP_Z2_PSWDLOCK : origin = 0x78210, length = 0x000004

/* Z2 OTP. CRCLOCK/RESERVED */

// DCSM_OTP_Z2_CRCLOCK : origin = 0x78214, length = 0x000004

/* Z2 OTP. GPREG3/BOOTCTRL */

// DCSM_OTP_Z2_BOOTCTRL : origin = 0x7821C, length = 0x000004

/* DCSM Z1 Zone Select Contents (!!Movable!!) */

/* Z2 OTP. Z2 password locations / Flash and RAM partitioning */

// DCSM_ZSEL_Z2_P0 : origin = 0x78220, length = 0x000010

RESET : origin = 0x003FFFC0, length = 0x00000002

BOOTROM : origin = 0x003F0000, length = 0x00008000

BOOTROM_EXT : origin = 0x003F8000, length = 0x00007FC0

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

GROUP { /* GROUP memory ranges for crc/checksum of entire flash */

#endif

#endif

#define DEBUG_MODE

#ifdef DEBUG_MODE

BEGIN : origin = 0x080000, length = 0x000010 // 上电能跑的程序引导地址。

#else

BEGIN : origin = 0x082010, length = 0x000010 // 需要bootload引导的地址。

#endif

/* Flash sectors */

/* BANK 0 */

#ifdef DEBUG_MODE

FLASH_BANK0_SEC1 : origin = 0x080010, length = 0x00EFF0 /* on-chip Flash */

#else

FLASH_BANK0_SEC1 : origin = 0x082020, length = 0x00CFE0 /* on-chip Flash */ // 需要bootload引导的地址。

#endif

// FLASH_BANK0_SEC1 : origin = 0x082000, length = 0x00D000 /* on-chip Flash */ // 上电能跑的程序引导地址。

// FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK0_SEC15_RSVD : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

} crc(_table_name, algorithm=C28_CHECKSUM_16)

#endif

#endif

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

b0_dcsm_otp_z1_linkpointer : > DCSM_OTP_Z1_LINKPOINTER PAGE = 0

b0_dcsm_otp_z1_gpreg : > DCSM_OTP_Z1_GPREG PAGE = 0

b0_dcsm_otp_z1_pswdlock : > DCSM_OTP_Z1_PSWDLOCK PAGE = 0

b0_dcsm_otp_z1_crclock : > DCSM_OTP_Z1_CRCLOCK PAGE = 0

b0_dcsm_otp_z1_bootctrl : > DCSM_OTP_Z1_BOOTCTRL PAGE = 0

b0_dcsm_zsel_z1 : > DCSM_ZSEL_Z1_P0 PAGE = 0

// b0_dcsm_otp_z2_linkpointer : > DCSM_OTP_Z2_LINKPOINTER PAGE = 0

// b0_dcsm_otp_z2_gpreg : > DCSM_OTP_Z2_GPREG PAGE = 0

// b0_dcsm_otp_z2_pswdlock : > DCSM_OTP_Z2_PSWDLOCK PAGE = 0

// b0_dcsm_otp_z2_crclock : > DCSM_OTP_Z2_CRCLOCK PAGE = 0

// b0_dcsm_otp_z2_bootctrl : > DCSM_OTP_Z2_BOOTCTRL PAGE = 0

// b0_dcsm_zsel_z2 : > DCSM_ZSEL_Z2_P0 PAGE = 0

// .text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4, ALIGN(8)

.text : >> FLASH_BANK0_SEC1 , ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS4567

.bss:output : > RAMLS4567

.bss:cio : > RAMGS0

.const : > FLASH_BANK0_SEC1, ALIGN(8)

.data : > RAMLS4567

.sysmem : > RAMLS4567

ramgs0 : > RAMGS0

/* Allocate IQ math areas: */

//IQmath : > RAMLS4567

//IQmathTables : > RAMLS4567

IQmath : > FLASH_BANK0_SEC1

IQmathTables : > FLASH_BANK0_SEC1

/*

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMGS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

*/

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMLS7,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

/* crc/checksum section configured as COPY section to avoid including in executable */

.TI.memcrc : type = COPY

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

MEMORY

{

ACCESSPROTECTION : origin = 0x0005F500, length = 0x0000003E

ADCA : origin = 0x00007400, length = 0x00000080

ADCC : origin = 0x00007500, length = 0x00000080

ADCARESULT : origin = 0x00000B00, length = 0x00000018

ADCCRESULT : origin = 0x00000B40, length = 0x00000018

ANALOGSUBSYS : origin = 0x0005D700, length = 0x00000100

BGCRCCPU : origin = 0x00006340, length = 0x00000040

CANA : origin = 0x00048000, length = 0x00000200

CLB1DATAEXCH : origin = 0x00003180, length = 0x00000080

CLB2DATAEXCH : origin = 0x00003580, length = 0x00000080

CLB1LOGICCFG : origin = 0x00003000, length = 0x00000052

CLB2LOGICCFG : origin = 0x00003400, length = 0x00000052

CLB1LOGICCTRL : origin = 0x00003100, length = 0x00000040

CLB2LOGICCTRL : origin = 0x00003500, length = 0x00000040

CLBXBAR : origin = 0x00007A40, length = 0x00000040

CLKCFG : origin = 0x0005D200, length = 0x00000100

CMPSS1 : origin = 0x00005C80, length = 0x00000020

CMPSS2 : origin = 0x00005CA0, length = 0x00000020

CMPSS3 : origin = 0x00005CC0, length = 0x00000020

CMPSS4 : origin = 0x00005CE0, length = 0x00000020

CPUTIMER0 : origin = 0x00000C00, length = 0x00000008

CPUTIMER1 : origin = 0x00000C08, length = 0x00000008

CPUTIMER2 : origin = 0x00000C10, length = 0x00000008

CPUSYS : origin = 0x0005D300, length = 0x000000A0

DCC0 : origin = 0x0005E700, length = 0x00000038

DCC1 : origin = 0x0005E740, length = 0x00000038

// DCSMBANK0Z1OTP : origin = 0x00078000, length = 0x00000020

DCSMBANK0Z1 : origin = 0x0005F000, length = 0x00000024

DCSMBANK0Z2OTP : origin = 0x00078200, length = 0x00000020

DCSMBANK0Z2 : origin = 0x0005F040, length = 0x00000024

DCSMCOMMON : origin = 0x0005F070, length = 0x00000010

DEVCFG : origin = 0x0005D000, length = 0x000001AC

DMACLASRCSEL : origin = 0x00007980, length = 0x0000001A

DMA : origin = 0x00001000, length = 0x00000200

ECAP1 : origin = 0x00005200, length = 0x00000020

ECAP2 : origin = 0x00005240, length = 0x00000020

ECAP3 : origin = 0x00005280, length = 0x00000020

EPWM1 : origin = 0x00004000, length = 0x00000100

EPWM2 : origin = 0x00004100, length = 0x00000100

EPWM3 : origin = 0x00004200, length = 0x00000100

EPWM4 : origin = 0x00004300, length = 0x00000100

EPWM5 : origin = 0x00004400, length = 0x00000100

EPWM6 : origin = 0x00004500, length = 0x00000100

EPWM7 : origin = 0x00004600, length = 0x00000100

EPWMXBAR : origin = 0x00007A00, length = 0x00000040

EQEP1 : origin = 0x00005100, length = 0x00000040

EQEP2 : origin = 0x00005140, length = 0x00000040

ERADCOUNTER1 : origin = 0x0005E980, length = 0x00000010

ERADCOUNTER2 : origin = 0x0005E990, length = 0x00000010

ERADCOUNTER3 : origin = 0x0005E9A0, length = 0x00000010

ERADCOUNTER4 : origin = 0x0005E9B0, length = 0x00000010

ERADCRCGLOBAL : origin = 0x0005EA00, length = 0x00000010

ERADCRC1 : origin = 0x0005EA10, length = 0x00000010

ERADCRC2 : origin = 0x0005EA20, length = 0x00000010

ERADCRC3 : origin = 0x0005EA30, length = 0x00000010

ERADCRC4 : origin = 0x0005EA40, length = 0x00000010

ERADCRC5 : origin = 0x0005EA50, length = 0x00000010

ERADCRC6 : origin = 0x0005EA60, length = 0x00000010

ERADCRC7 : origin = 0x0005EA70, length = 0x00000010

ERADCRC8 : origin = 0x0005EA80, length = 0x00000010

ERADGLOBAL : origin = 0x0005E800, length = 0x00000014

ERADHWBP1 : origin = 0x0005E900, length = 0x00000008

ERADHWBP2 : origin = 0x0005E908, length = 0x00000008

ERADHWBP3 : origin = 0x0005E910, length = 0x00000008

ERADHWBP4 : origin = 0x0005E918, length = 0x00000008

ERADHWBP5 : origin = 0x0005E920, length = 0x00000008

ERADHWBP6 : origin = 0x0005E928, length = 0x00000008

ERADHWBP7 : origin = 0x0005E930, length = 0x00000008

ERADHWBP8 : origin = 0x0005E938, length = 0x00000008

FLASH0CTRL : origin = 0x0005F800, length = 0x00000182

FLASH0ECC : origin = 0x0005FB00, length = 0x00000028

FSIRXA : origin = 0x00006680, length = 0x00000050

FSITXA : origin = 0x00006600, length = 0x00000050

GPIOCTRL : origin = 0x00007C00, length = 0x00000200

GPIODATAREAD : origin = 0x00007F80, length = 0x00000010

GPIODATA : origin = 0x00007F00, length = 0x00000040

HIC : origin = 0x00006500, length = 0x00000080

HRCAP3 : origin = 0x000052A0, length = 0x00000020

I2CA : origin = 0x00007300, length = 0x00000022

I2CB : origin = 0x00007340, length = 0x00000022

INPUTXBAR : origin = 0x00007900, length = 0x00000020

CLBINPUTXBAR : origin = 0x00007960, length = 0x00000020

LINA : origin = 0x00006A00, length = 0x000000EC

LINB : origin = 0x00006B00, length = 0x000000EC

MEMORYERROR : origin = 0x0005F540, length = 0x00000040

MEMCFG : origin = 0x0005F400, length = 0x000000C0

NMIINTRUPT : origin = 0x00007060, length = 0x00000010

OUTPUTXBAR : origin = 0x00007A80, length = 0x00000040

CLBOUTPUTXBAR : origin = 0x00007BC0, length = 0x00000040

SYSPERIPHAC : origin = 0x0005D500, length = 0x00000200

PIECTRL : origin = 0x00000CE0, length = 0x0000001A

PIEVECTTABLE : origin = 0x00000D00, length = 0x00000200

PMBUSA : origin = 0x00006400, length = 0x00000020

SCIA : origin = 0x00007200, length = 0x00000010

SPIA : origin = 0x00006100, length = 0x00000010

SPIB : origin = 0x00006110, length = 0x00000010

SYNCSOC : origin = 0x00007940, length = 0x00000006

WD : origin = 0x00007000, length = 0x0000002C

XBAR : origin = 0x00007920, length = 0x00000020

XINT : origin = 0x00007070, length = 0x0000000C

}

SECTIONS

{

/*** PIE Vect Table and Boot ROM Variables Structures ***/

UNION run = PIEVECTTABLE

{

PieVectTableFile

GROUP

{

EmuKeyVar

EmuBModeVar

EmuBootPinsVar

FlashCallbackVar

FlashScalingVar

}

}

AccessProtectionRegsFile : > ACCESSPROTECTION, type=NOINIT

AdcaRegsFile : > ADCA, type=NOINIT

AdccRegsFile : > ADCC, type=NOINIT

AdcaResultRegsFile : > ADCARESULT, type=NOINIT

AdccResultRegsFile : > ADCCRESULT, type=NOINIT

AnalogSubsysRegsFile : > ANALOGSUBSYS, type=NOINIT

BgcrcCpuRegsFile : > BGCRCCPU, type=NOINIT

CanaRegsFile : > CANA, type=NOINIT

Clb1DataExchRegsFile : > CLB1DATAEXCH, type=NOINIT

Clb2DataExchRegsFile : > CLB2DATAEXCH, type=NOINIT

Clb1LogicCfgRegsFile : > CLB1LOGICCFG, type=NOINIT

Clb2LogicCfgRegsFile : > CLB2LOGICCFG, type=NOINIT

Clb1LogicCtrlRegsFile : > CLB1LOGICCTRL, type=NOINIT

Clb2LogicCtrlRegsFile : > CLB2LOGICCTRL, type=NOINIT

ClbXbarRegsFile : > CLBXBAR, type=NOINIT

ClkCfgRegsFile : > CLKCFG, type=NOINIT

Cmpss1RegsFile : > CMPSS1, type=NOINIT

Cmpss2RegsFile : > CMPSS2, type=NOINIT

Cmpss3RegsFile : > CMPSS3, type=NOINIT

Cmpss4RegsFile : > CMPSS4, type=NOINIT

CpuTimer0RegsFile : > CPUTIMER0, type=NOINIT

CpuTimer1RegsFile : > CPUTIMER1, type=NOINIT

CpuTimer2RegsFile : > CPUTIMER2, type=NOINIT

CpuSysRegsFile : > CPUSYS, type=NOINIT

Dcc0RegsFile : > DCC0, type=NOINIT

Dcc1RegsFile : > DCC1, type=NOINIT

// DcsmBank0Z1OtpRegsFile : > DCSMBANK0Z1OTP, type=NOINIT

DcsmBank0Z1RegsFile : > DCSMBANK0Z1, type=NOINIT

DcsmBank0Z2OtpRegsFile : > DCSMBANK0Z2OTP, type=NOINIT

DcsmBank0Z2RegsFile : > DCSMBANK0Z2, type=NOINIT

DcsmCommonRegsFile : > DCSMCOMMON, type=NOINIT

DevCfgRegsFile : > DEVCFG, type=NOINIT

DmaClaSrcSelRegsFile : > DMACLASRCSEL, type=NOINIT

DmaRegsFile : > DMA, type=NOINIT

ECap1RegsFile : > ECAP1, type=NOINIT

ECap2RegsFile : > ECAP2, type=NOINIT

ECap3RegsFile : > ECAP3, type=NOINIT

EPwm1RegsFile : > EPWM1, type=NOINIT

EPwm2RegsFile : > EPWM2, type=NOINIT

EPwm3RegsFile : > EPWM3, type=NOINIT

EPwm4RegsFile : > EPWM4, type=NOINIT

EPwm5RegsFile : > EPWM5, type=NOINIT

EPwm6RegsFile : > EPWM6, type=NOINIT

EPwm7RegsFile : > EPWM7, type=NOINIT

EPwmXbarRegsFile : > EPWMXBAR, type=NOINIT

EQep1RegsFile : > EQEP1, type=NOINIT

EQep2RegsFile : > EQEP2, type=NOINIT

EradCounter1RegsFile : > ERADCOUNTER1, type=NOINIT

EradCounter2RegsFile : > ERADCOUNTER2, type=NOINIT

EradCounter3RegsFile : > ERADCOUNTER3, type=NOINIT

EradCounter4RegsFile : > ERADCOUNTER4, type=NOINIT

EradCRCGlobalRegsFile : > ERADCRCGLOBAL, type=NOINIT

EradCRC1RegsFile : > ERADCRC1, type=NOINIT

EradCRC2RegsFile : > ERADCRC2, type=NOINIT

EradCRC3RegsFile : > ERADCRC3, type=NOINIT

EradCRC4RegsFile : > ERADCRC4, type=NOINIT

EradCRC5RegsFile : > ERADCRC5, type=NOINIT

EradCRC6RegsFile : > ERADCRC6, type=NOINIT

EradCRC7RegsFile : > ERADCRC7, type=NOINIT

EradCRC8RegsFile : > ERADCRC8, type=NOINIT

EradGlobalRegsFile : > ERADGLOBAL, type=NOINIT

EradHWBP1RegsFile : > ERADHWBP1, type=NOINIT

EradHWBP2RegsFile : > ERADHWBP2, type=NOINIT

EradHWBP3RegsFile : > ERADHWBP3, type=NOINIT

EradHWBP4RegsFile : > ERADHWBP4, type=NOINIT

EradHWBP5RegsFile : > ERADHWBP5, type=NOINIT

EradHWBP6RegsFile : > ERADHWBP6, type=NOINIT

EradHWBP7RegsFile : > ERADHWBP7, type=NOINIT

EradHWBP8RegsFile : > ERADHWBP8, type=NOINIT

Flash0CtrlRegsFile : > FLASH0CTRL, type=NOINIT

Flash0EccRegsFile : > FLASH0ECC, type=NOINIT

FsiRxaRegsFile : > FSIRXA, type=NOINIT

FsiTxaRegsFile : > FSITXA, type=NOINIT

GpioCtrlRegsFile : > GPIOCTRL, type=NOINIT

GpioDataReadRegsFile : > GPIODATAREAD, type=NOINIT

GpioDataRegsFile : > GPIODATA, type=NOINIT

HicRegsFile : > HIC, type=NOINIT

HRCap3RegsFile : > HRCAP3, type=NOINIT

I2caRegsFile : > I2CA, type=NOINIT

I2cbRegsFile : > I2CB, type=NOINIT

InputXbarRegsFile : > INPUTXBAR, type=NOINIT

ClbInputXbarRegsFile : > CLBINPUTXBAR, type=NOINIT

LinaRegsFile : > LINA, type=NOINIT

LinbRegsFile : > LINB, type=NOINIT

MemoryErrorRegsFile : > MEMORYERROR, type=NOINIT

MemCfgRegsFile : > MEMCFG, type=NOINIT

NmiIntruptRegsFile : > NMIINTRUPT, type=NOINIT

OutputXbarRegsFile : > OUTPUTXBAR, type=NOINIT

ClbOutputXbarRegsFile : > CLBOUTPUTXBAR, type=NOINIT

SysPeriphAcRegsFile : > SYSPERIPHAC, type=NOINIT

PieCtrlRegsFile : > PIECTRL, type=NOINIT

PieVectTableFile : > PIEVECTTABLE, type=NOINIT

PmbusaRegsFile : > PMBUSA, type=NOINIT

SciaRegsFile : > SCIA, type=NOINIT

SpiaRegsFile : > SPIA, type=NOINIT

SpibRegsFile : > SPIB, type=NOINIT

SyncSocRegsFile : > SYNCSOC, type=NOINIT

WdRegsFile : > WD, type=NOINIT

XbarRegsFile : > XBAR, type=NOINIT

XintRegsFile : > XINT, type=NOINIT

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/